前回のプログラムにおいて、TileLinkがどのような動きをしているのか確認してみる。

あるキャッシュブロックを取得する際、L2キャッシュはBチャネルを使ってProbeコマンドを送り、そのブロックを持っているキャッシュに対してそのブロックを取得するためのコマンドを送出するようだ。

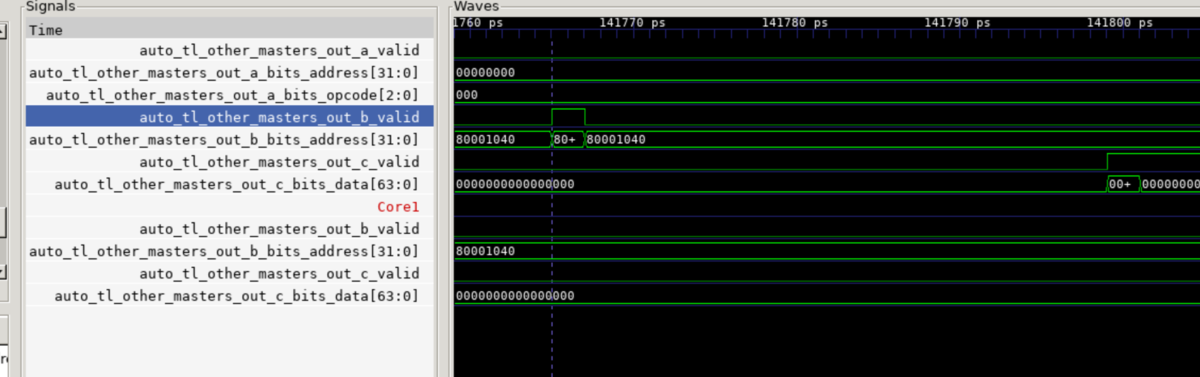

以下の図は、BチャネルによるキャッシュブロックのProbeに対するCチャネルでのレスポンスを示している。

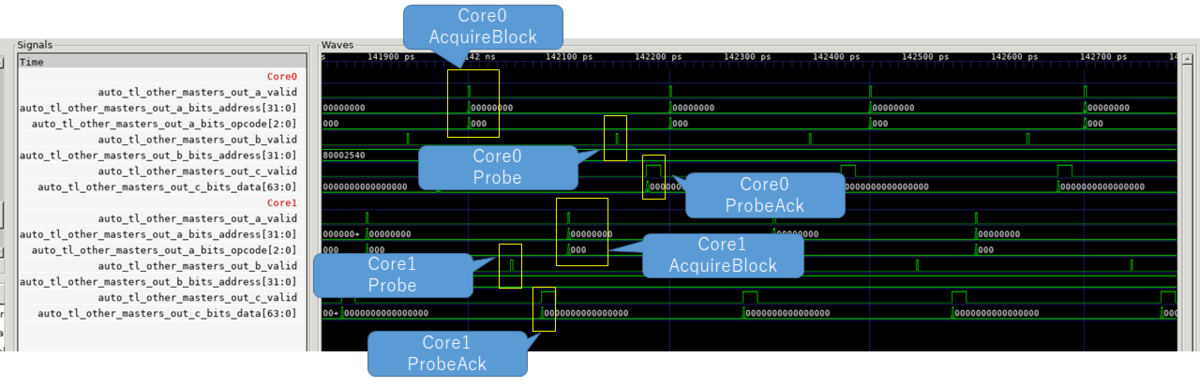

キャッシュブロックを取り合う様子を見てみようと思う。データの更新回数を1000回にして、その間にブロックがコア間を行きかうのを見てみようと思う。

void slave_main(int hartid) { // printf ("hartid = %d\n", hartid); for (int i = 0; i < 1000; i++) { false_share_data.core_data[hartid]++; } __asm__ __volatile__ ("amoadd.w x0, %0, (%1)": :"r"(1), "r"(&finish_wait)); while(finish_wait != 2); // printf("core_data[%d] = %d\n", hartid, false_share_data.core_data[hartid]); }

こんな感じで、各コアでブロックを取り合っているのが分かると思う。