ChipyardでRTLシミュレーションを行う場合、波形を出力する場合にはdebugターゲットを使ってコンパイルすることになる。

Verilatorを使う場合にはデフォルトで出力される波形フォーマットはVCDなのだが、VCDはテキストフォーマットのため波形を出力すると巨大なファイルが生成されてしまいディスクを圧迫する。

VerilatorがサポートしているVCD以外の波形フォーマットとしてFSTがある。FSTはFast Signal Traceの略で、VCDがテキストフォーマットであるのに対してFSTはバイナリフォーマットであるためディスクを圧迫せずに便利だ。GtkWaveの波形表示の際にもローディングの時間が省略できて便利なので、なるべくVCDは使わずにFSTだけで済ませたい。

ChipyardのVerilator用シミュレーション環境にそういう設定がないのかなと思い色々探していると、一応そのためのマクロが切ってあるようだった。

ChipyardのVerilator用シミュレーションのTopにあたるC++環境はchipyard/generators/utilities/src/main/resources/csrc/emulator.ccに格納されている。

このファイルを見てみると、一応FSTのためのマクロが作ってあるようだった。

chipyard/generators/utilities/src/main/resources/csrc/emulator.cc

#if CY_FST_TRACE #include "verilated_fst_c.h" #else #include "verilated.h" #include "verilated_vcd_c.h" /* ... 中略 ... */ #if VM_TRACE Verilated::traceEverOn(true); // Verilator must compute traced signals #if CY_FST_TRACE std::unique_ptr<VerilatedFstC> tfp(new VerilatedFstC); #else std::unique_ptr<VerilatedVcdFILE> vcdfd(new VerilatedVcdFILE(vcdfile)); std::unique_ptr<VerilatedVcdC> tfp(new VerilatedVcdC(vcdfd.get())); #endif // CY_FST_TRACE

なるほど、CY_FST_TRACEというdefineを有効にすればFSTを作れそうな気がしている。このマクロはどこで制御されているのかというと、

sims/verilator/Makefile

80:TRACING_CFLAGS := $(if $(filter $(VERILATOR_FST_MODE),0),,-DCY_FST_TRACE)

なるほど、VERILATOR_FST_MODEを有効化すればこのマクロが有効になるらしい。

$ cd sims/verilator/ $ make debug CONFIG=MediumBoomConfig VERILATOR_FST_MODE=1

これでシミュレーションバイナリを作ってみた。一応コンパイルは成功する。--helpを表示してみた。

EMULATOR OPTIONS -c, --cycle-count Print the cycle count before exiting +cycle-count -h, --help Display this help and exit -m, --max-cycles=CYCLES Kill the emulation after CYCLES +max-cycles=CYCLES -s, --seed=SEED Use random number seed SEED -r, --rbb-port=PORT Use PORT for remote bit bang (with OpenOCD and GDB) If not specified, a random port will be chosen automatically. -V, --verbose Enable all Chisel printfs (cycle-by-cycle info) +verbose -v, --vcd=FILE, Write vcd trace to FILE (or '-' for stdout) -x, --dump-start=CYCLE Start VCD tracing at CYCLE +dump-start

オプションは相変わらず--vcdとなっているが、これでも一応FSTが生成されるのだろうか?以下のようにしてシミュレーションを実行してみる。

$ ./simulator-chipyard-MediumBoomConfig-debug \ --vcd=coremark.medium.vcd \ --verbose \ ../../software/coremark/riscv-coremark/coremark.bare.riscv 2>&1 | tee coremark.medium.opt.mtune.log

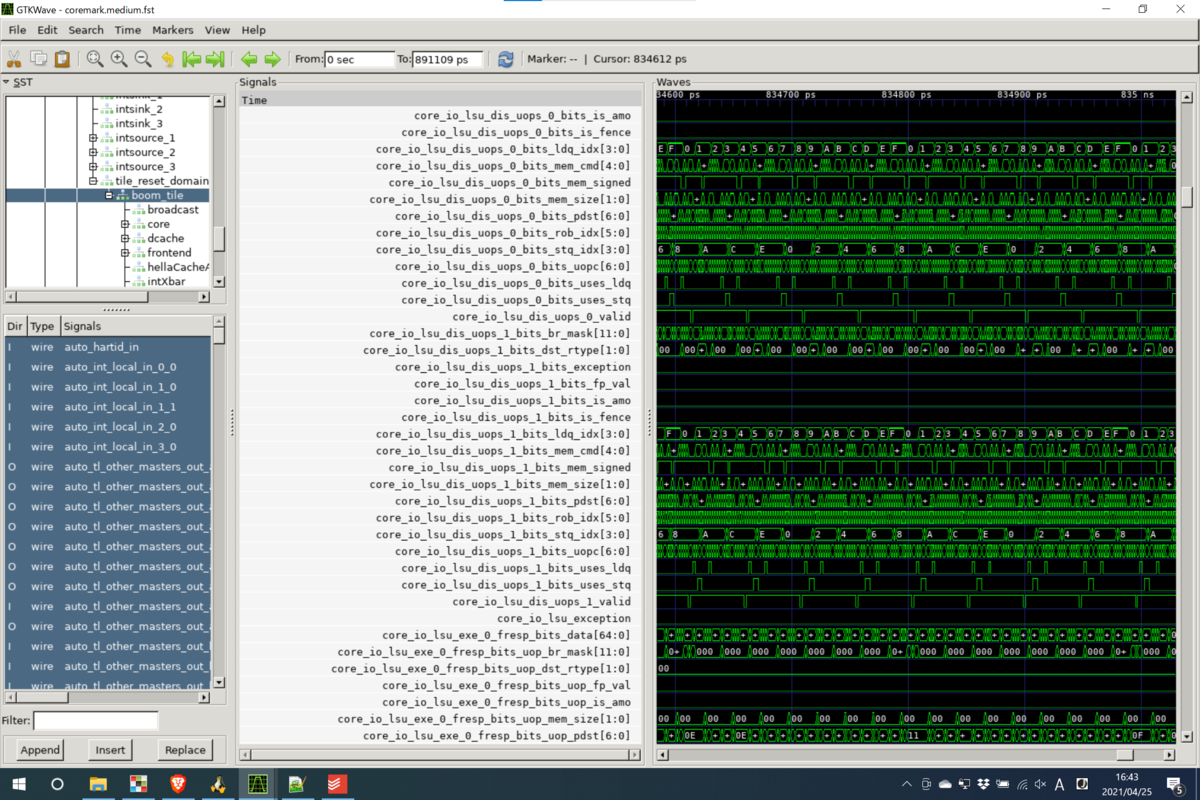

上記のコマンドでcoremark.medium.vcdが生成されたが、これはVCDではなくFSTファイルのようだった。リネームしてGTKWaveで開いてみる。

$ mv coremark.medium.vcd coremark.medium.fst

GTKWaveできちんと表示することができた。FSTなのでファイルサイズも小さく、これからはこのモードを使っていくことにしよう。