5.5 2ステージアドレス変換

現在の仮想モードVが1であるときは常に2ステージアドレス変換と保護が有効である。すべての仮想メモリアクセスにおいて、オリジナルの仮想アドレスはvsatpレジスタにより制御されるVSレベルアドレス変換によって最初のステージで変換され、ゲスト物理アドレスとなる。ゲスト物理アドレスは次にhgatpレジスタにより制御されるゲスト物理アドレスに変換され、スーパーバイザー物理アドレスに変換される。この2つのステージはVSステージ変換とGステージ変換と呼ばれる。V=1の際にこれらの2ステージアドレス変換を無効化する方法はないが、該当するvsatpかhgatpのレジスタをゼロに設定することにより効率的にどちらかの変換を無効化することができる。

vsstatusのMXRフィールドは実行可能フラグのみ設定されているページを読み込み可能にすることができるが、これはVSステージのページ保護にのみ有効である。VSレベルでのMXRの設定はゲスト物理ページ保護の設定をオーバーライドしない。HSレベルでのMXRの設定では、VSステージとGステージ両方の実行可能フラグについてオーバーライドされる。

V=1では、アドレス変換を通常バイパスするメモリアクセスはGステージのアドレス変換のみを実行する目的がある。これはvSレベルのページの読み書きなど、VSステージアドレス変換のサポートも含まれる。

マシンレベルの物理メモリ保護については仮想モードの状態に関係なくスーパーバイザ物理アドレスにも適用される。

5.5.1 ゲスト物理アドレス変換

ゲスト物理アドレスからスーパーバイザー物理アドレスへの変換は、hgatp(5.2.9節) CSRレジスタにより制御される。

アドレス変換のスキームであるhgatpのMODEフィールドでBareが設定されている場合、ゲスト物理アドレスとスーパーバイザー物理アドレスは全く変換されず同一であり、ゲスト物理アドレスからスーパーバイザ物理アドレスの変換中にメモリ保護は適用されない。

hgatp.MODEがSv32x4, Sv39x4, Sv48v4が選択されたとき、Gステージアドレス変換は通常の仮想アドレス変換のスキームであるSv32, Sv39, Sv48に相当するものである。個々の場合において、やってくるアドレスのサイズは2ビットずつ広げられる(34ビット、41ビット、50ビット)。2つの余分なビットにより、ルートページテーブル(のみ)がサイズを通常の4KiBから16KiBに拡張される。大きなサイズにマッチさせるために、ルートページテーブルは4KiBのページ境界ではなく16KiBのアドレス境界に配置されている必要がある。このことを除けば、Gステージの変換は通常のSv32, Sv39, Sv48と他の機能については何の違いもない。ルートページテーブルではないページ、そしてすべてのページテーブルエントリ(PTE)は4.3節, 4.4節, 4.5節で説明されているものと同一である。

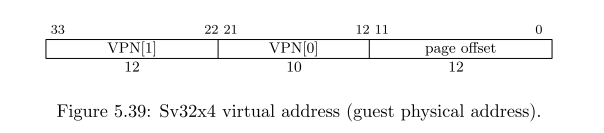

Sv32x4では、やってくるゲスト物理アドレスは図5.39に示すように仮想ページ番号(VPN)とページオフセットに分割される。この分割方法はSv32における図4.15(73ページ)の分割方法と同一であるが、VPN[1]の上位に2ビット追加されているところが異なる(ゲスト物理アドレスの分割されたフィールドは、図4.16に示されるSv32が割り当てる物理アドレスの構造にそれぞれ相当している)。

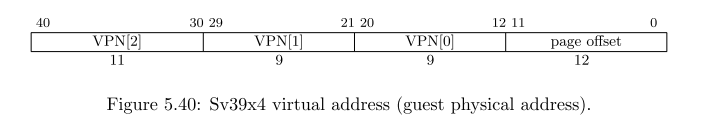

Sv39x4では、やってくるゲスト物理アドレスは図5.40に示すように仮想ページ番号(VPN)とページオフセットに分割される。この分割方法はSv39における図4.18(77ページ)の分割方法と同一であるが、VPN[2]の上位に2ビット追加されているところが異なる。ビット63:41はゼロでなくてはならず、そうでなければゲストページフォルト例外が発生する。

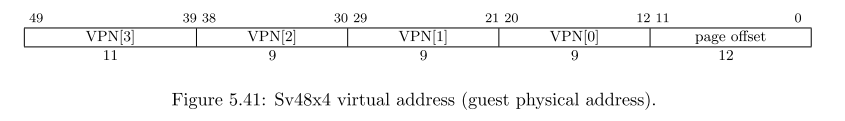

Sv48x4では、やってくるゲスト物理アドレスは図5.41に示すように仮想ページ番号(VPN)とページオフセットに分割される。この分割方法はSv48における図4.31(78ページ)の分割方法と同一であるが、VPN[3]の上位に2ビット追加されているところが異なる。ビット63:50はゼロでなくてはならず、そうでなければゲストページフォルト例外が発生する。

RV32用のページベースのGステージアドレス変換方式Sv32x4は、34ビットのゲスト物理アドレスをサポートするように定義されており、RV32ハイパーバイザーが33ビットや34ビットの物理アドレスを持つ実在の32ビットRISC-Vマシンを仮想化する能力を制限する必要がない。これには、マシンが33ビットまたは34ビットの物理アドレスを使用している場合に、マシン自体を仮想化する可能性も含まれる。ルートページテーブルのサイズとアラインメントを4倍にすることは、Sv32を34ビットのアドレスをカバーするように拡張する最も安価な方法である。不必要に大きいルートページテーブルのために12KiBを無駄にする可能性があるが、ほとんどの(おそらくすべての)実際の用途では無視できるほどの影響はないと考えられる。

物理アドレス空間の4倍の仮想アドレス空間を持つマシンを仮想化する一貫した機能は、RV64でも有用であると考えられている。例えば、39ビットの仮想アドレス(Sv39)を実装したマシンの場合、これにより、48ビットの仮想アドレス(Sv48)をハードウェアでサポートする必要も、シャドウページテーブルを使用してより大きなアドレス空間をエミュレートする必要もなく、ハイパーバイザー拡張は最大41ビットのゲスト物理アドレス空間をサポートすることができる。

Sv32x4, Sv39x4, Sv48x4のゲスト物理アドレスは4.3.2節で説明されているSv32, Sv39, Sv48と同じアルゴリズムによって変換されるが、例外として:

Gステージのアドレス変換では、すべてのメモリアクセス(VSステージアドレス変換のためのデータ構造へのアクセスも含む)はユーザレベルでのアクセスであると考えられ、U-Modeであるかのように実行される。アクセスタイプのパーミッションー読み込み可能、書き込み可能、実行可能ーについてはGステージアドレス変換中にも、VSステージの変換と同様に実行される。VSステージのアドレス変換のために行われるメモリアクセス(VSレベルページテーブルへのアクセスなど)については、パーミッションはオリジナルのアクセスタイプとは違いロードストア処理としてチェックされる。しかしすべての例外はオリジナルのアクセスタイプ(命令フェッチ、ロード、ストア/AMO)として通知される。

Gステージアドレス変換は、Gステージ変換と通常のHSレベルアドレス変換の間で、いくつかの(またはすべての)ページテーブルを共有する可能性があるため、Uビットを含めても、通常のアドレス変換と同じフォーマットをPTEに使用する。この使用法が一般的になるかどうかにかかわらず、我々はこれを除外しないことにした。