Western DigitalからオリジナルのRISC-VコアSweRVがリリースされた。

2019/06/20追記。Swerv-EH1 CoreはCHIPS Allianceプロジェクトのサブプロジェクトとして正式にGitHubのリポジトリが移された。Swerv-EH 1.1が公開されている。

https://github.com/westerndigitalcorporation/swerv_eh1

基本的なスペックは以下の通り。これはSweRVの資料から引っ張ってきた。

https://github.com/westerndigitalcorporation/swerv_eh1/tree/master/docs

- サポートアーキテクチャ : RV32IMCZifencei_Zicsr

- 4wayセットアソシアティブ命令キャッシュ(パリティとECCをサポート)をオプションでサポート

- 255個の外部割込みをサポートするプログラマブル割り込みコントローラをオプションでサポート

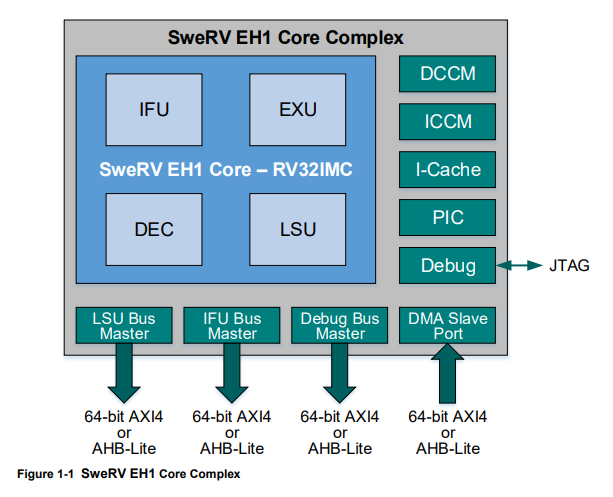

- システムバスインタフェースは4種類 : 命令フェッチ、データアクセス、デバッグアクセス、TCM向けの外部DMA

- 64-bit幅のAXIか、AHB-Liteをサポート

- RISC-Vデバッグ仕様に基づいたコアデバッグユニットをサポート

- 28nmプロセスで1GHz動作をターゲットとする。

仕様を読む限りはハイパフォーマンス向けでは無く、コントローラ用途のマイコンに思える。仕様的にも結構手を加えている印象。

以下の図は同資料から引用。内部のコンポーネントとインタフェースについて。

ビルド方法

cd ${HOME}/work/riscv/

git clone https://github.com/westerndigitalcorporation/swerv_eh1.git

export RV_ROOT=${HOME}/work/riscv/swerv_eh1

このRV_ROOTという変数は必ず必要らしい。ここからはコンフィグレーションを設定する。

$ ${RV_ROOT}/configs/swerv.config -h Main configuration database for SWERV This script documents, and generates the {`#} define/include files for verilog/assembly/backend flows User options: -target = { default} use default settings for one of the targets -set=var=value set arbitrary variable to a value -unset=var unset any definitions for var -snapshot=name name the configuration (only if no -target specified) Additional direct options for the following variables: ...

ちなみに、DCCMはData Closely Coupled Memory(=DTCM)のことらしい。TCMのことか。 ICCMはInstruction Closely Coupled Memory(=ICTM)でもある。

とりあえずデフォルトで構成した。

${RV_ROOT}/configs/swerv.config swerv: Using target "default" swerv: target = default swerv: ret_stack_size = 4 swerv: btb_size = 32 swerv: bht_size = 128 swerv: dccm_enable = 1 swerv: dccm_region = 0xf swerv: dccm_offset = 0x80000 swerv: dccm_size = 32 swerv: dccm_num_banks = 8 swerv: iccm_enable = 0 swerv: iccm_region = 0xe swerv: iccm_offset = 0xe000000 swerv: iccm_size = 512 swerv: iccm_num_banks = 8 swerv: icache_enable = 1 swerv: icache_ecc = 0 swerv: icache_size = 16 swerv: pic_2cycle = 0 swerv: pic_region = 0xf swerv: pic_offset = 0x100000 swerv: pic_size = 32 swerv: pic_total_int = 8 swerv: lsu_stbuf_depth = 8 swerv: lsu_wrbuf_depth = 4 swerv: dma_buf_depth = 2 swerv: lsu_num_nbload = 4 swerv: dec_instbuf_depth = 4 swerv: opensource = 1 swerv: no_secondary_alu = 0 swerv: Writing /home/msyksphinz/work/riscv/swerv_eh1/configs/snapshots/default/common_defines.vh swerv: Writing /home/msyksphinz/work/riscv/swerv_eh1/configs/snapshots/default/defines.h swerv: Writing /home/msyksphinz/work/riscv/swerv_eh1/configs/snapshots/default/pd_defines.vh swerv: Writing /home/msyksphinz/work/riscv/swerv_eh1/configs/snapshots/default/whisper.json swerv: Writing /home/msyksphinz/work/riscv/swerv_eh1/configs/snapshots/default/perl_configs.pl

これで、コンフィグレーションを決めるための以下のファイルが生成されるようだ。それぞれ、RTL用、C言語プログラミング用、ポストレイアウト用などのファイルが生成されている。

$RV_ROOT/configs/snapshots/default ├── common_defines.vh # `defines for testbench or design ├── defines.h # #defines for C/assembly headers ├── pd_defines.vh # `defines for physical design ├── perl_configs.pl # Perl %configs hash for scripting ├── pic_ctrl_verilator_unroll.sv # Unrolled verilog based on PIC size ├── pic_map_auto.h # PIC memory map based on configure size └── whisper.json # JSON file for swerv-iss

この後Verilatorでコンパイルできるのだが、テストベンチとテストプログラム類も同梱されていないのでどうも先に進めない。 自分で用意しろってことか。 どうもアドレスマップもRocketとはずいぶん異なるようで、Rocketのテストベンチのバイナリをそのまま動かすことはできないような気がする。

ソースコードの中身を見てみたが、SystemVerilogと言いつつ随分と前時代的で、なんだタダのVerilogじゃん、という気がしなくもない。 まあ広く一般に公開するんだから、SystemVerilogの難しい構文を使われるとツールによってはコンパイルできないのでありがたい、と考えることもできる。

Vivadoで論理合成をしてみよう

リグレッション環境が存在しないので少し触るのに時間がかかりそうだが、せっかくなのでVivadoを使って論理合成を行ってみたい。

論理合成の環境も用意されていない。自分で作ることにした。 Vivadoに読み込ませるべきファイルリストは、designディレクトリに存在するflistを参考に作成した。

$RV_ROOT/syn/filelist.tcl

read_verilog -sv ../design/swerv_wrapper.sv read_verilog -sv ../design/mem.sv read_verilog -sv ../design/pic_ctrl.sv read_verilog -sv ../design/swerv.sv ...

どうにかして論理合成が終わった。動作周波数は50MHzくらいかな? Zynq