前回、RISC-V Rocket-Chip を使って、コアの基本体力である命令のレイテンシ・スループットを測定する環境作成に取り掛かった。

整数命令についてはおおよそ測定できるようになった。次は浮動小数点命令だ。四則演算など、基本的なところから手を付けて行きたい。

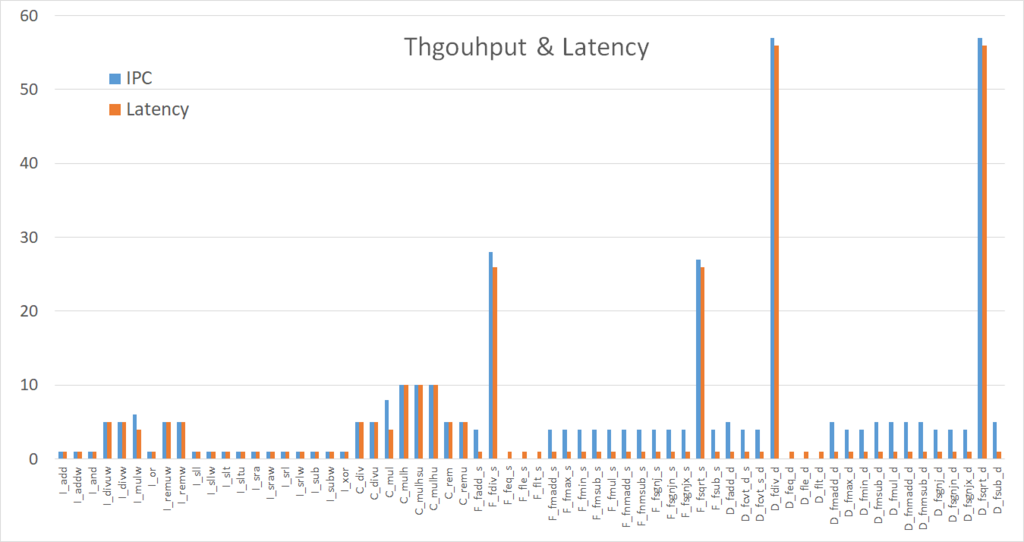

とりあえず、パタンジェネレータを作成して、代表的な命令の性能を測定する環境を構築した。 - 同じ命令を384回 (=6x64回) 実行して、その時にかかるサイクル数を測定。そこからレイテンシとスループットを推定。 - 以下の結果は、シミュレーション結果から推定した値を四捨五入した。このため実際には厳密ではない可能性がある。

この中で Rocket-Chip の性能について分かったことは以下の通りだ。

| IPC | Latency | |

|---|---|---|

| I_add | 1 | 1 |

| I_addw | 1 | 1 |

| I_and | 1 | 1 |

| I_divuw | 5 | 5 |

| I_divw | 5 | 5 |

| I_mulw | 6 | 4 |

| I_or | 1 | 1 |

| I_remuw | 5 | 5 |

| I_remw | 5 | 5 |

| I_sll | 1 | 1 |

| I_sllw | 1 | 1 |

| I_slt | 1 | 1 |

| I_sltu | 1 | 1 |

| I_sra | 1 | 1 |

| I_sraw | 1 | 1 |

| I_srl | 1 | 1 |

| I_srlw | 1 | 1 |

| I_sub | 1 | 1 |

| I_subw | 1 | 1 |

| I_xor | 1 | 1 |

| C_div | 5 | 5 |

| C_divu | 5 | 5 |

| C_mul | 8 | 4 |

| C_mulh | 10 | 10 |

| C_mulhsu | 10 | 10 |

| C_mulhu | 10 | 10 |

| C_rem | 5 | 5 |

| C_remu | 5 | 5 |

| F_fadd_s | 4 | 1 |

| F_fdiv_s | 28 | 26 |

| F_feq_s | 0 | 1 |

| F_fle_s | 0 | 1 |

| F_flt_s | 0 | 1 |

| F_fmadd_s | 4 | 1 |

| F_fmax_s | 4 | 1 |

| F_fmin_s | 4 | 1 |

| F_fmsub_s | 4 | 1 |

| F_fmul_s | 4 | 1 |

| F_fnmadd_s | 4 | 1 |

| F_fnmsub_s | 4 | 1 |

| F_fsgnj_s | 4 | 1 |

| F_fsgnjn_s | 4 | 1 |

| F_fsgnjx_s | 4 | 1 |

| F_fsqrt_s | 27 | 26 |

| F_fsub_s | 4 | 1 |

| D_fadd_d | 5 | 1 |

| D_fcvt_d_s | 4 | 1 |

| D_fcvt_s_d | 4 | 1 |

| D_fdiv_d | 57 | 56 |

| D_feq_d | 0 | 1 |

| D_fle_d | 0 | 1 |

| D_flt_d | 0 | 1 |

| D_fmadd_d | 5 | 1 |

| D_fmax_d | 4 | 1 |

| D_fmin_d | 4 | 1 |

| D_fmsub_d | 5 | 1 |

| D_fmul_d | 5 | 1 |

| D_fnmadd_d | 5 | 1 |

| D_fnmsub_d | 5 | 1 |

| D_fsgnj_d | 4 | 1 |

| D_fsgnjn_d | 4 | 1 |

| D_fsgnjx_d | 4 | 1 |

| D_fsqrt_d | 57 | 56 |

| D_fsub_d | 5 | 1 |