- 作者: John L. Hennessy,David A. Patterson

- 出版社/メーカー: Morgan Kaufmann

- 発売日: 2017/12/07

- メディア: ペーパーバック

- この商品を含むブログを見る

7.7章は DSAの一つの例としてPixel Visual Coreを取り上げている。

あまりネット上で見たことのない情報が公開されているが、参考文献はどこなのだろうか? あるいは、David.A Patterson 先生はGoogleにも所属しているので、そこからの情報なのかな。 用語集とか、かなりありがたい。

目次

- 7.1章 イントロダクション

- 7.2章 DSAのガイドライン

- 7.3章 DSAの用語集

- 7.3章 DNNのニューロン・トレーニングと推論

- 7.3章 多層パーセプトロン、畳み込みニューラルネットワーク、再帰型ニューラルネットワーク

- 7.4章 Google's Tensor Processing Unit

- 7.5章 Microsoft Catapult, フレキシブルなデータセンタアクセラレータ

- 7.6章 Intel Crest, 学習のためのデータセンタアクセラレータ

- 7.7章 Pixel Visual Core, パーソナルモバイル画像処理ユニット)

これは著者が読んだ内容をまとめているだけなので、誤訳、理解不足により誤っている可能性があります!鵜呑みにしないようにお願いします。

7.7章 Pixel Visual Core, パーソナルモバイル画像処理ユニット

Pixel Visual CoreもGoogleの開発したモバイル向けのDSAユニットである。 これは、コンピュータビジョン処理に最適化したDSAであり、携帯電話やタブレット上のチップとして、Androidによって制御されるk、音を想定している。

マルチコアのデザインになっており、2から16コアの構成をサポートしており、TPUというよりもSystem on Chip(SOC)として動作することを想定している。

モバイル向けのためTPUよりも構成としては非常に小さく、消費電力も小さく構成されている。

Pixel Visual Coreについて理解するために、まずは用語集を作成した。この用語を参照しながら解説を読み進めていってほしい。

| 用語 | 略語 | 簡単な説明 |

|---|---|---|

| コア | プロセッサ。Pixel Visual Coreは2~16コアを持っている。最初の実装では8コアが使われた。これは「ステンシルプロセッサ(Stencil Processor:STP)」とも呼ばれている。 | |

| Halide | 画像処理向けのドメイン固有プログラミング言語で。アルゴリズムの形式と実行スケジュールを分離することを目的としている。 | |

| Halo | 16×16の計算アレイにおいてステンシル計算を実行するにあたり、アレイの境界に近い場所を拡張した領域。この領域は値を持っているが、計算はしない。 | |

| 画像信号処理プロセッサ | ISP | 画像の品質を向上させるための固定機能を持ったASIC。カメラを搭載しているすべてのPMDで見つけることができる。 |

| 画像処理ユニット | IPU | GPUと逆の問題を解決するためのDSA。入力画像を解析しコントラストなどを変更することで出力画像を生成する。 |

| Line Buffer Pool | LB | ラインバッファ処理中の画像を中間結果を格納し、次のステージをすぐに実行することができるようにするためのバッファ。すべてのラインを保持できるように、十分な大きさを用意している。 |

| ネットワークオンチップ | NOC | Pixel Visual Core内のコアを接続するためのネットワーク |

| 物理ISA | pISA | ハードウェアで実行される、Pixel Visual Coreの命令セットアーキテクチャ(ISA) |

| プロセッシングエレメントアレイ | 16×16のプロセッシングエレメントとhaloによって処理される16bitの積和演算。各プロセッシングエレメントには、ベクトルレーンとローカルメモリが搭載されている。4方向のどちらにも、データをシフトして転送することができる。 | |

| シートジェネレータ | SHG | 1×1から31×31ピクセルのブロックのメモリアクセスのことを「シート」と呼ぶ。Haloの領域を搭載するかを含めて、他のサイズはオプションである。 |

| スカラーライン | SCL | ベクトルレーンと演算としては同一なのだが、ジャンプ、分岐、例外、生後命令によりベクトルアレイを制御できる命令が加わっていることが異なる。すべてのシートジェネレータのロードストアをスケジュール管理する。小さな命令メモリも含んでいる。スカラプロセッサ中のベクトルアーキテクチャと同じような役割である。 |

| ベクトルレーン | VL | プロセッシングエレメントの一部分で、計算を行う。 |

| 仮想ISA | vISA | コンパイラによって生成されるPixel Visual CoreのISA。命令実行前に、物理ISAにマッピングされる。 |

Pixel Visual Coreは新しいクラスのドメイン固有アーキテクチャで、画像処理のために画像処理ユニット(Image Processing Unit:IPU)というものを搭載している。 IPUはGPUと逆の問題を解決するためのDSAで、入力画像を解析しコントラストなどを変更することで出力画像を生成する。 IPUはDSAなので、CPUやGPUなどが、DSAが苦手とする領域の処理を行ってくれるためすべての処理をDSAで実行する必要はない。 IPUはCNNの項目で開設した、CNN計算に依存している。

Pixel Visual Coreの新しいところは、SIMD命令のような1次元の処理だけでなく、2次元の処理も実行できるようになっている点である。 PEのネットワークは2次元で構成されており、これによりオフチップのメモリにアクセスする必要性も最小化される。 このアーキテクチャにより、CNNアルゴリズムや画像処理の中心であるステンシル計算を、ハードウェアを使ってシンプルに実行することができるようになる。

ハードワイヤードなIPUであるISP

カメラを搭載しているモバイルデバイス(Personal Mobile Device: PMD)には必ず、ハードワイヤードなアクセラレータであるISP(Image Signal Processor)が搭載されている。 ISPは固定機能を持ったASICで、仮想的にすべてのISPに搭載されている。

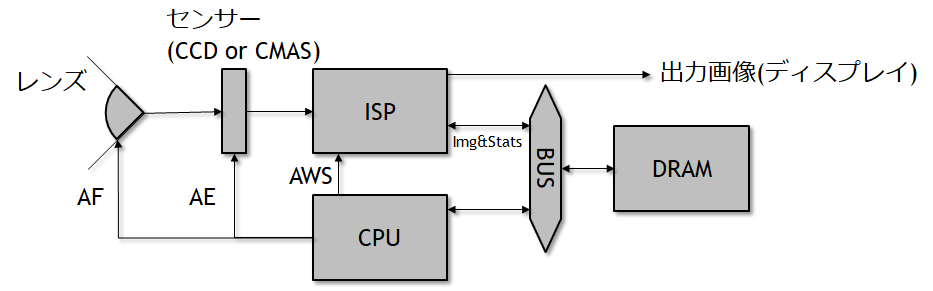

図7.30は基本的な画像処理システムの構成を示している。 画像処理システムには、レンズ、センサー、ISP、CPU、DRAM、ディスプレイなどが搭載されている。 ISPは画像を受け取ると、レンズとセンサーから人工物を除去し失われた色を補完する。 そして、全体的な画像の品質を向上させる。 PMDは小さなレンズを使うのでピクセルにゴミが乗りやすくなり、したがって高い品質の画像とビデオを生成するためにはこれらの処理は不可欠である。

図7.30 一般的な画像処理プロセッサの構成。画像処理プロセッサ(ISP)、CPU、DRAM、レンズ、センサで構成されている。

ISPプロセッサはハードウェアビルディングブロックをソフトウェアでコンフィグレーションしながら処理を進める。 一般的には、各ステージをパイプライン化してメモリトラフィックを最小化するように設計され、少しのピクセルを入力し、少しのピクセルを出力する。 計算内容は主に隣接したピクセルとのステンシル計算であるが、これらの計算の結果は「ラインバッファ」と呼ばれるバッファに格納される。 ラインバッファにより隣接するピクセルの局所性を使用して、中間画像を保持することによってすべてのラインをキャプチャ氏、中間結果を次のステージに転送することができる。

ISPは効率的であるが、2つの問題点がある。 ポータブルデバイスの処理能力が向上するにつれ、画像の品質は向上していき、ISPのフレキシビリティの無さが問題となってくる。 特に新しいISPをSOC上に設計するためには、数年の歳月を要することになる。 2つ目の問題は、この計算リソースが、画像の品質を向上させるためだけに利用されるということである。 これはPMDにおいて常に必要とされる処理ではない。 現在の世代のISPは高性能向けのPMDでは2Tops/sの処理を実行することができ、DSAに置き換えても同様の処理能力と効率性を達成することができる。

Pixel Visual Coreのソフトウェア

Pixel Visual Coreを一般的なハードワイヤードなパイプライン構成と考えると、ISPと同様に有効非巡回グラフ(directed acyclic graph:DAG)に落とし込むことができる。 Pixel Visual Coreの画像処理プログラムは一般的にHalideで記述される。 Halideはドメイン固有向けの関数型プログラミング言語で、画像処理に適している。 図7.31に画像をぼかす処理をHalideで記述した例を示す。 Halideはプログラムの機能を示す領域と、プログラムのスケジューリングを行う領域を分離して記述することができ、ハードウェア上で機能をどのようにして最適化するかを指定することができる。

Func buildBlur(Func input)

// 機能記述領域 (ターゲットプロセッサとは独立している)

Func blur_x("blur_x"), blur_y("blur_y");

blur_x(x,y) = (input(x-1,y) + input(x,y)*2 + input(x+1,y))/4;

blur_y(x,y) = (input(x,y-1) + input(x,y)*2 + input(x,y-1))/4;

if (has_ipu) {

// スケジューリングの領域(ターゲットプロセッサに対してどのように最適化を行えばよいかを示している)

blur_x.ipu(x,y)

blur_y.ipu(x,y)

}

return blur_y;

}

図7.31 画像をぼかす処理をHalideで記述した例

Pixel Visual Coreのアーキテクチャ哲学

Pixel Visual CoreはPMDデバイスで実行されるため、10~20秒で6~8Wを消費し、スクリーンが消されると10mW程度に消費電力が減る。 これらのPMDの消費電力に対応するため、Pixel Visual Coreは相対的なエネルギーコストにおいて調査を行っており、図7.32に示す。 単一の8-bit DRAMアクセスは、12,500個の8-bit加算もしくは7~100回の8-bit SRAMアクセスと同一の消費電力である。 また、IEEE 754の浮動小数点演算のコストは8-bitの整数演算の22倍から150倍の電力を消費し、ダイサイズは大きくなる。

| 操作 | エネルギー(pJ) | 操作 | エネルギー(pJ) | 操作 | エネルギー(pJ) |

|---|---|---|---|---|---|

| 8b DRAM LPDDR3 | 125.00 | 8b SRAM | 1.2-17.1 | 16b SRAM | 2.4-34.2 |

| 32b Fl. Pt. muladd | 2.70 | 8b int muladd | 0.12 | 16b int muladd | 0.43 |

| 32b Fl. Pt. add | 1.50 | 8b int add | 0.01 | 16b int add | 0.02 |

操作ごとのエネルギーコスト。TSMC 28-nm HPMプロセスでの測定結果。このプロセスはPixel Visual Coreで実際に使用している。

7.2章のガイドラインに加えて、Pixel Visual Coreは以下の観点により設計されている。

- 2次元は1次元の構成よりも良い

- 2次元の構成により、画像処理にのデータコミュニケーションの距離を最小化することができる。

- 遠いよりは、近いほうが良い: データの移動は高価である

- さらに、データをALUに移動するコストも増加する。DRAMの処理時間とエネルギーコストは、ローカルストレージでのデータ移動に比べるとずっと高い。

IPUの目的は、ハードウェアプログラマビリティを与えることにより画像処理以外の用途にも使うことができるようにすることだ。 Pixel Visual Coreには以下の3つの用途がある。

- 2次元構成は1次元の構成よりも優れているという考え方により、Pixel Visual Coreは2次元のSIMDアーキテクチャを採用している。

- 2次元アレイ上にプロセッシングエレメント(PE)を配置している。

- PEは以下の要素で構成される。

16-bitというデータ幅は、このドメインで必要なデータ精度を考慮したうえで決定されている。

Pixel Visual Coreは各PEに一時記憶保存が必要である。PEのメモリはコンパイラにより制御されるスクラッチパッドメモリである。PEメモリの論理的なサイズは、16bit×128エントリで、256バイトである。各PEに分離した小さなSRAMを搭載することは実装的に非効率なため、Pixel Visual CoreはPEメモリを8つのPEでグループ化し、1つの幅広いSRAMブロックとして構成している。

- PEはSIMDの形式で処理するため、Pixel Visual Coreはすべての読み込みと書き込みの処理をまとめてSRAMにリクエスト薄ことができる。

- これはより小さな複数個のSRAMを使うよりも効率的である。

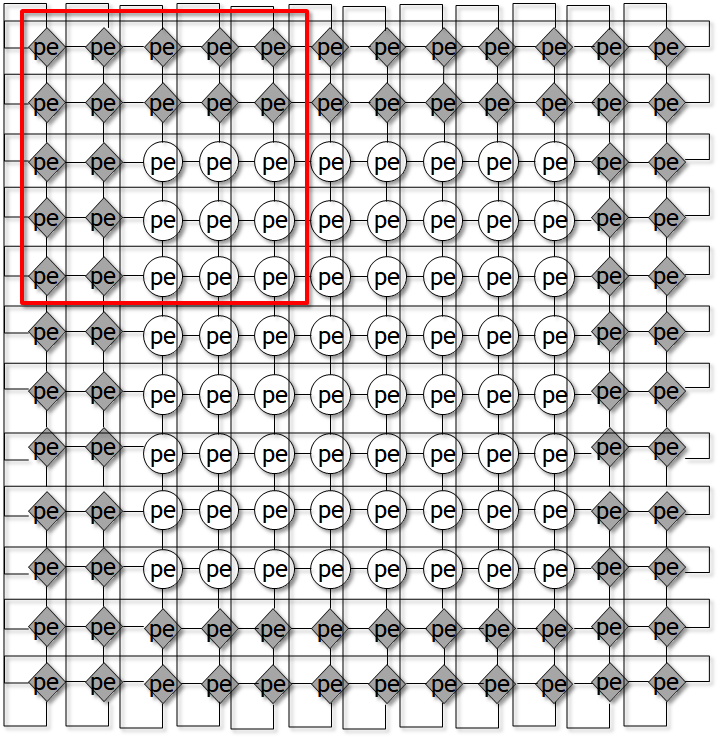

図7.33に4つのPEの例を示している。

すべてのPEで同時にステンシル計算を実行するため、Pixel Visual Coreは隣接するPEから入力データを集める必要がある。

- このために、NSEW(North, South East West)のネットワークを持っている。

- PE間でデータを任意の方向にシフトすることができ、このため画像をシフトして行っても、画像が端でロストすることはない。

- Pixel Visual Coreはネットワークの一番後ろでトーラス構造をとっている。

ソフトウェアは明示的にデータを所望の方向に移動させることができる。 一方でハードウェアによって制御される死すトリックアレイは、2次元のパイプラインは一方にのみ転送され、ソフトウェアからは見ることができない。

Pixel Visual CoreのHalo

3×3、5×5、7×7のステンシルでは、入力データとして1、2、3個の余分なピクセルを入力する。 Pixel Visual Coreは、

- 入力値のみを渡すために境界付近でハードウェアを利用する。

- ALUを除去した単純なPEを使ってわずかに2次元コアを拡張する。

単純なPEと通常のPEは2.2倍の面積の違いがあるため、Pixel Visual Coreは8×8のPEの外に2行2列のPEを拡張している。 この拡張された領域をhaloと呼んでいる。 図7.34は2行2列の拡張を行っており、左上で5×5のステンシル計算を行っている。

図7.34 Pixel Visual Coreの2次元アレイは、中央のPEと周囲のHaloと呼ばれるシンプルなPEコアで構成されている。

Pixel Visual Coreのプロセッサ

16×16個のPEと1次元当たり4つのHaloによって、PEアレイもしくはベクトルアレイと呼ばれ、Pixel Visual Coreの主要な計算ユニットである。 シートジェネレータ(Sheet Generator: SHG)というロードストアユニットを持っている。 SHGは1×1から256×256ピクセルのブロックのメモリ中で参照することができる。

Pixel Visual Core内部は2コア以上のPEを含んでいるので、PE間はNOCで接続されている。 NOCは基本的に隣接PEとの接続する構成となっている。 このNOCは2次元メッシュ状に構成されている。

Pixel Visual Coreはスカラレーンというプロセッサも持っている。 このスカラレーンは、ベクトルアレイに普通のプロセッサのように、ジャンプ、分岐、割り込み、命令制御フローなどの処理を実行してはならない。 このスカラレーンは小さな命令メモリを持っており、これはスカラプロセッサのSIMD命令のフローに似ている。

さらに、Pixel Visual CoreはDMAエンジンを持っており、DRAMとラインバッファの転送を高速に実行することができる。