RISC-VのRocket Chipで、FPGAにインプリメンテーションをするためにはいくつかの方法があるが、その中でfpga-zynqリポジトリ(https://github.com/ucb-bar/fpga-zynq)を使って、FPGAにRISC-Vを焼いてみている。

その中で、やはりRoCC(Rocket Custom Coprocessor)を使った実験をいろいろ行っているため、RoCCのアクセラレータ付きでのRocket Chip構成をFPGAにビルドしてみたい。

そのため、前回は、RoccZynqConfigという構成を新たに作成して、FPGAのビルドを行ってみた。前回までで、とりあえずVivadoでのビルドは完了した。

次はLinuxをブートするための各種ファイルの生成とビルドだ。

RISC-Vの動作するLinuxは、既に生成済みのものが提供されている。詳細は、fpga-zynqリポジトリのREADME.md (https://github.com/ucb-bar/fpga-zynq) を参考にしてほしいが、

“2) Pushing Your Rocket Modifications to the FPGA"で、Vivadoのプロジェクトを作成する。 "3) Building Everything from Scratch"で、各種必要なFSBLや、Linuxのビルドを行う。

最終的に、以下のようなファイル構成が完成する。これをSDカードにコピーして、ZedBoardからブートさせるということだ。

SD_ROOT/ |-> boot.bin |-> devicetree.dtb |-> uImage |-> uramdisk.image.gz

ちなみに、"3) Building Everything from Scratch"を一つ一つステップを踏んでいかなくても、make CONFIG=RoccZynqConfig で一気に実行できるみたい?良く分からない。

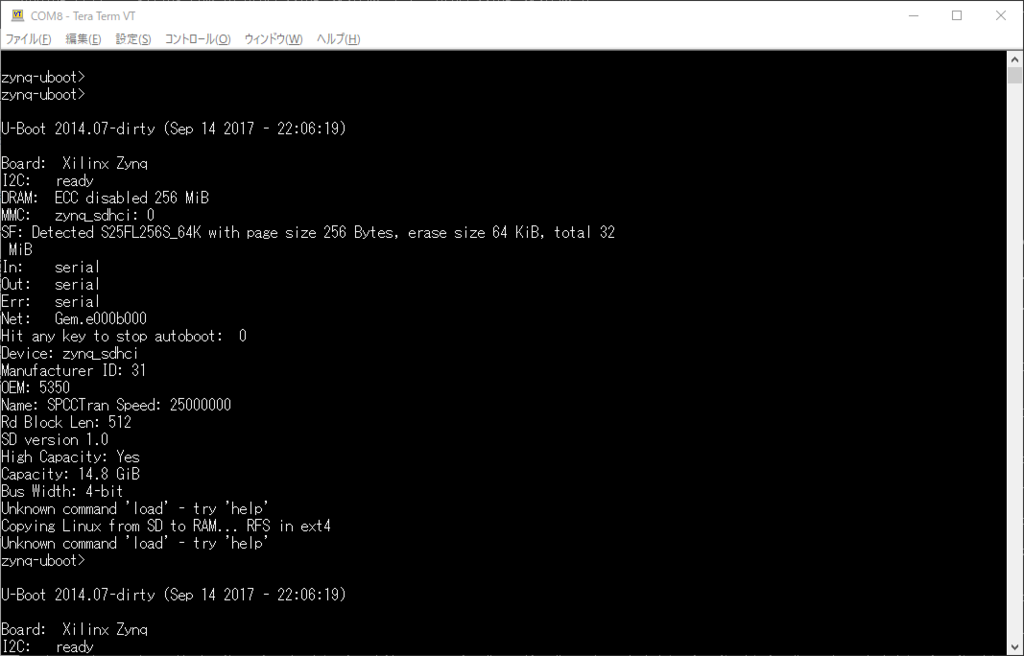

ファイル群をSDカードにコピーして、ブートしてみたのだが、以下のようなメッセージが出てどうやらARM上のLinuxがブートしない。

とりあえずなんだか分からないので、ほかに方法はあったはずだといろいろ調べ、以下のウェブサイトを見つけた。

ここに書いてある、以下のコマンドシーケンスを実行するとLinuxがブートされる。

fatload mmc 0 0x3000000 uImage fatload mmc 0 0x2A00000 devicetree.dtb fatload mmc 0 0x2000000 uramdisk.image.gz bootm 0x3000000 0x2000000 0x2A00000

そこで、fpga-zynqの説明にあるように、RISC-Vプロセッサをフロントエンドから制御してみようと思ったのだが、どうも上手く行かない。

つまり、サンプルプログラムを実行させても、固まって応答が無くなってしまうのだ。

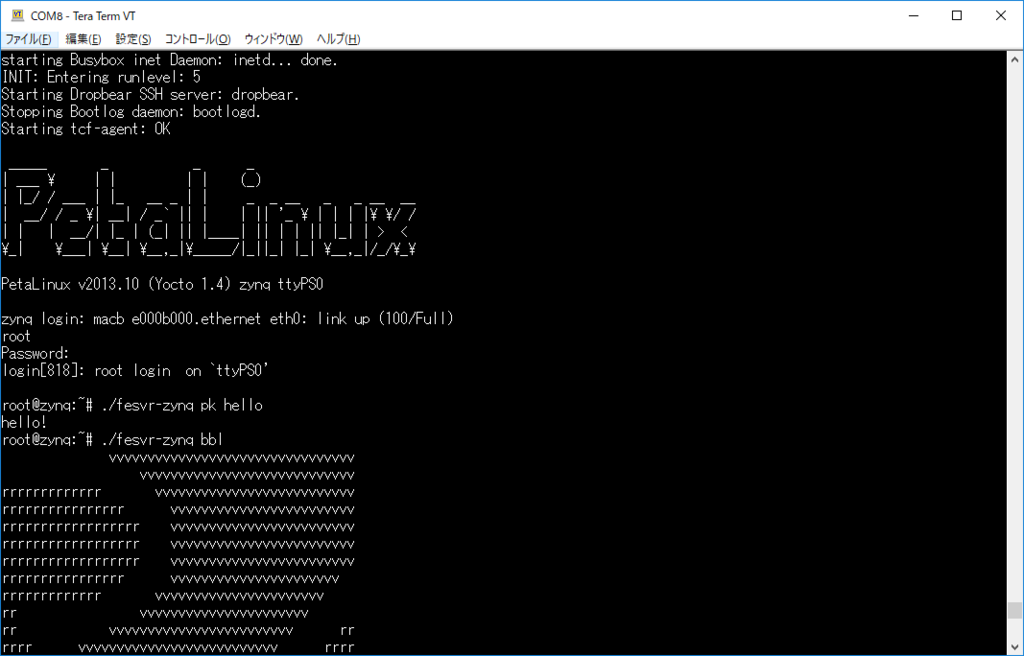

./fesvr-zynq pk hello (応答なし) ./fesvr-zynq bbl (応答なし)

おかしいので、構成を元に戻して (CONFIG=ZynqConfigで再合成)、再びFPGAボードに書き込んで同じようにテストをすると正しく動作した。何が違うんだろうなあ。。

これは継続して調査が必要だ。