RISC-Vプロセッサの実装もちょっと手詰まりになってきたので、少し気分転換に、他のプロセッサはどのように実装されているんだろう、というのが気になった。

フリーで入手できるそこそこ高性能なプロセッサとしては、OpenSPARCか、RISC-VのBOOMが存在するが、内部を解析するということを考えるとBOOMは高位合成言語で記述されているということもあり不向きであると考えた。

そこで、ちょっとした気分転換にOpenSPARC T2を触ってみようと考えた。

OpenSPARCとは

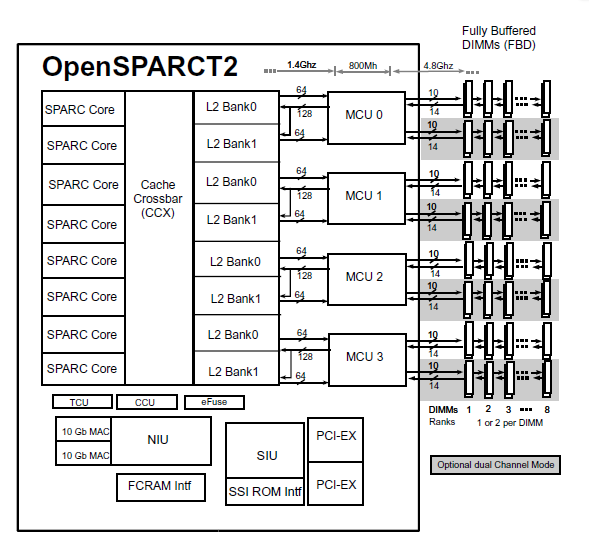

Sun Microsystems(現在はOracle)のSPARCプロセッサのオープンコア版。2006年に公開されたT1、2008年に公開されたT2が存在しているが、今回はT2に焦点を当てる。

- 8スレッドSMT

- 最大8コア搭載で、合計64スレッド実行

- 各コアについては

OpenSPARCをダウンロードして中身を調査する

OpenSPARCは以下のサイトからダウンロードできる。

Overview of OpenSPARC Resources

で、肝心の中身なのだが、ほぼ10年前のデザインということもあり、趣味で扱うにはなかなか障壁が高い。

などなど、実行させるまでにかなり時間がかかる。どうにかしてModelsimで動作させることが出来ないかと調査していたのだが、よくよく観察するとファイルリストがきちんと収録されている。

~/work/t2 $ find . -name "*flist" ./design/fpga/gate/fpga_gate_tb.flist ./design/fpga/gate/xilinx_lib.flist ./design/fpga/rtl/fpga_rtl.flist ./design/fpga/rtl/fpga_rtl_synth.flist ./design/sys/iop/ccu/ccu.flist ./design/sys/iop/ccx/ccx.flist ./design/sys/iop/ccx/ccx_rtl.flist ...

なるほど、これらを連結していって、Modelsimでオリジナルの環境を構成すればよい気がしている。./verif/env/cmp/cmp.flistがどうやら中心のファイルになるかな?

// Testbench Files for cmp Bench +define+OPENSPARC_CMP+ +incdir++ +incdir+../common/verilog/checkers+ +incdir+../common/verilog/misc+ +incdir+../common/coverage+ +libext+.v+ cmp_top.v verif_args.v -y ../../../libs/analog/n2_esd_core_cust_l/n2_esd_core_cust/rtl -y ../../../libs/analog/n2_pcmb_cust_l/n2_pcmb_cust/rtl -y ../../../libs/analog/n2_pcma_cust_l/n2_pcma_cust/rtl -y ../../../libs/analog/n2_tmpd_cust_l/n2_tmpd_cust/rtl -y ../../../libs/analog/n2_rng_cust_l/n2_rng_cust/rtl -y ../../../libs/analog/n2_revid_cust_l/n2_revid_cust/rtl -y ../../../libs/clk/n2_clk_gl_cust_l/n2_clk_gl_cust/rtl -y ../../../libs/clk/n2_clk_pgrid_cust_l/n2_clk_spc_cmp_cust/rtl -y ../../../libs/n2sram/mp/n2_frf_mp_256x78_cust_l/n2_frf_mp_256x78_cust/rtl -y ../../../libs/tisram/core/n2_icd_sp_16p5kb_cust_l/n2_icd_sp_16p5kb_cust/rtl -y ../../../libs/tisram/core/n2_ict_sp_1920b_cust_l/n2_ict_sp_1920b_cust/rtl -y ../../../libs/n2sram/dp/n2_dva_dp_32x32_cust_l/n2_dva_dp_32x32_cust/rtl -y ../../../libs/n2sram/tlbs/n2_tlb_tl_64x59_cust_l/n2_tlb_tl_64x59_cust/rtl -y ../../../libs/n2sram/mp/n2_irf_mp_128x72_cust_l/n2_irf_mp_128x72_cust/rtl

定義やオプションなども一通り含まれているので、とりあえずこれを使えば大丈夫そうだ。