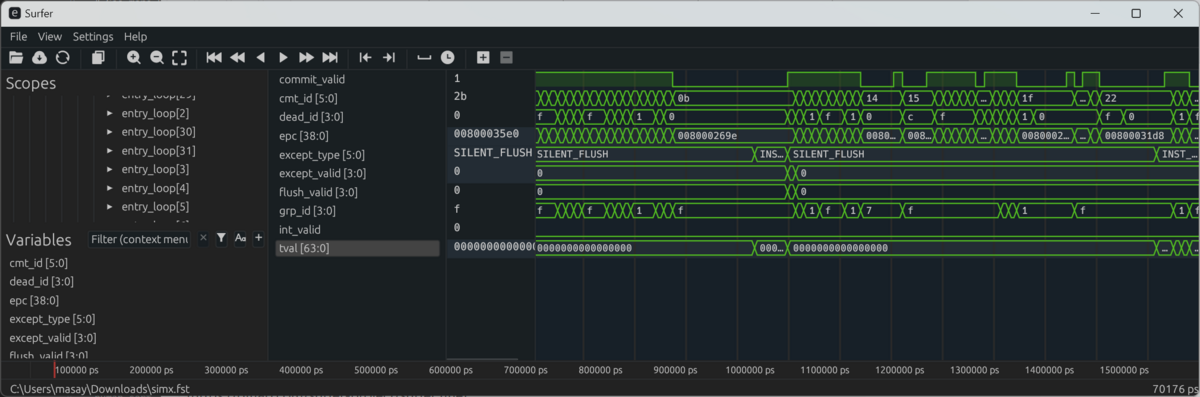

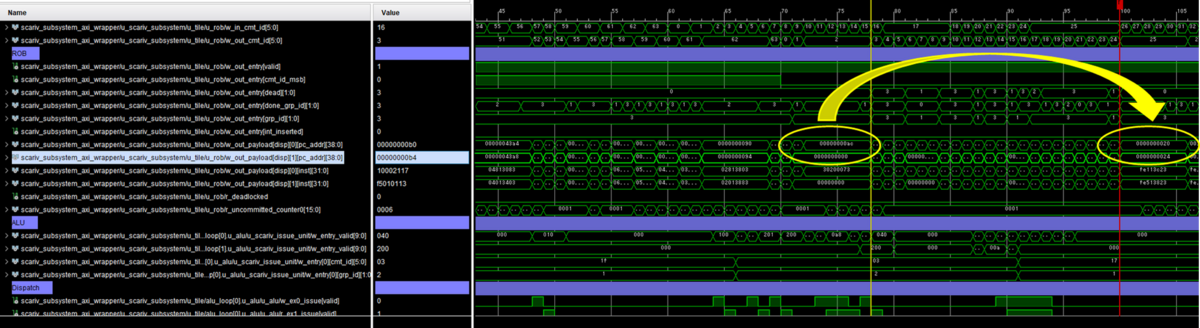

0x28付近でループしている。これは例外処理の部分。

0000000000000020 <trap_entry>: 20: fe113c23 sd ra,-8(sp) 24: fe513823 sd t0,-16(sp) 28: fe613423 sd t1,-24(sp) 2c: fe713023 sd t2,-32(sp) 30: fca13c23 sd a0,-40(sp) 34: fcb13823 sd a1,-48(sp) 38: fcc13423 sd a2,-56(sp) 3c: fcd13023 sd a3,-64(sp) 40: fae13c23 sd a4,-72(sp) 44: faf13823 sd a5,-80(sp) 48: fb013423 sd a6,-88(sp) 4c: fb113023 sd a7,-96(sp) 50: f9c13c23 sd t3,-104(sp) 54: f9d13823 sd t4,-112(sp) 58: f9e13423 sd t5,-120(sp) 5c: f9f13023 sd t6,-128(sp) 60: f8010113 add sp,sp,-128 64: 78d030ef jal 3ff0 <isr> 68: 07813083 ld ra,120(sp) 6c: 07013283 ld t0,112(sp) 70: 06813303 ld t1,104(sp) 74: 06013383 ld t2,96(sp) 78: 05813503 ld a0,88(sp) 7c: 05013583 ld a1,80(sp) 80: 04813603 ld a2,72(sp) 84: 04013683 ld a3,64(sp) 88: 03813703 ld a4,56(sp) 8c: 03013783 ld a5,48(sp) 90: 02813803 ld a6,40(sp) 94: 02013883 ld a7,32(sp) 98: 01813e03 ld t3,24(sp) 9c: 01013e83 ld t4,16(sp) a0: 00813f03 ld t5,8(sp) a4: 00013f83 ld t6,0(sp) a8: 08010113 add sp,sp,128 ac: 30200073 mret

ずっと割り込みルーチンを回っている気がする。

0xac → 0x20 をずっと回っている気がする。

なんで0x64の飛び先が毎回変わっているんだ?

左のobjdumpでは、0x64が0x3ff0に飛んでいるが、initファイルは、

fb013423 fb113023 f9c13c23 f9d13823 f9e13423 f9f13023 f8010113 2e8040ef # 0x64 ずれている? 07813083 07013283 06813303 06013383 05813503 05013583 04813603

なんでこれがずれるんだ?

再合成して、もう一度アセンブリコードを作り直し:

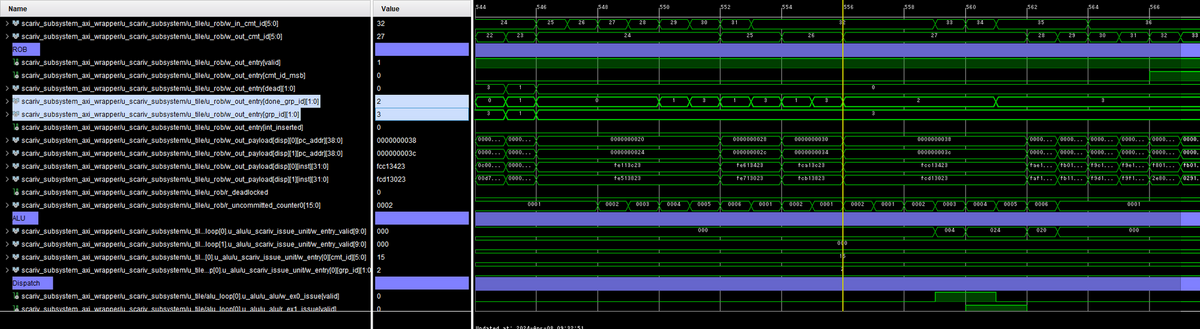

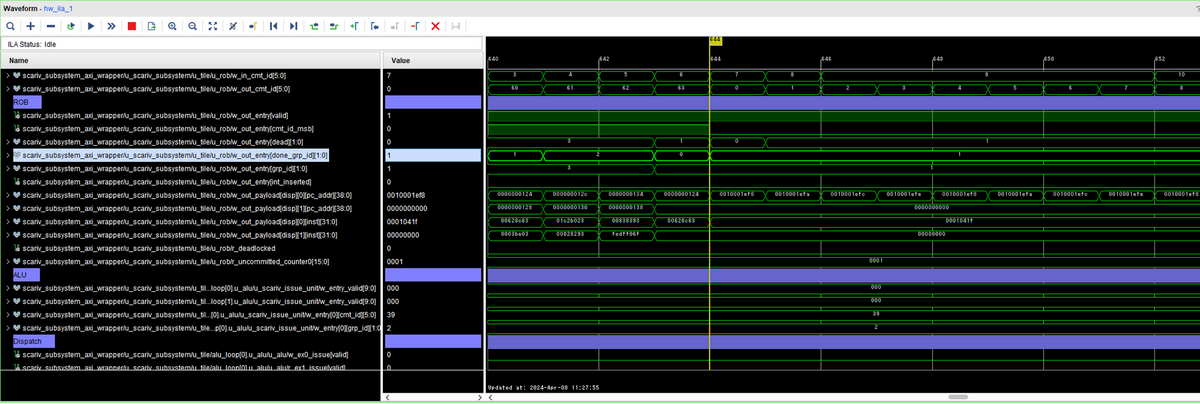

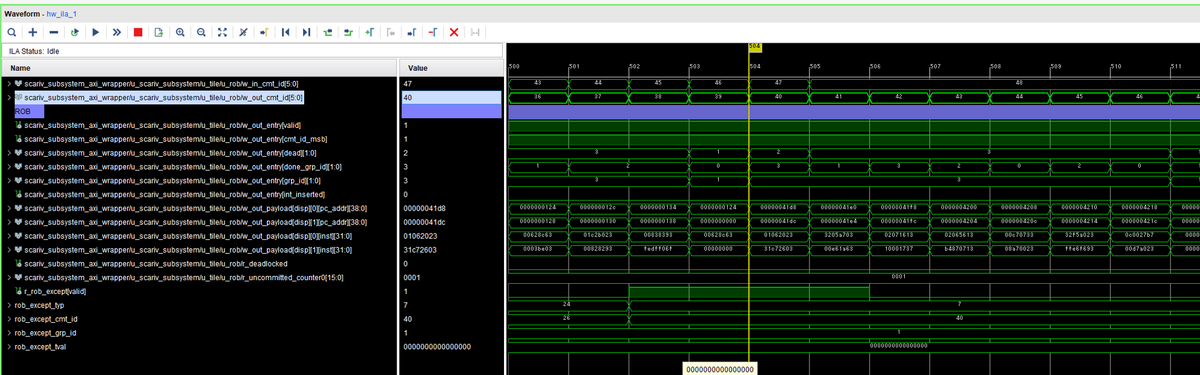

mretからの戻りが、0x10001ef8などという意味不明なアドレスからになっている。

0xac(mret)からの戻りが、どうして0x20になっているのだろう?

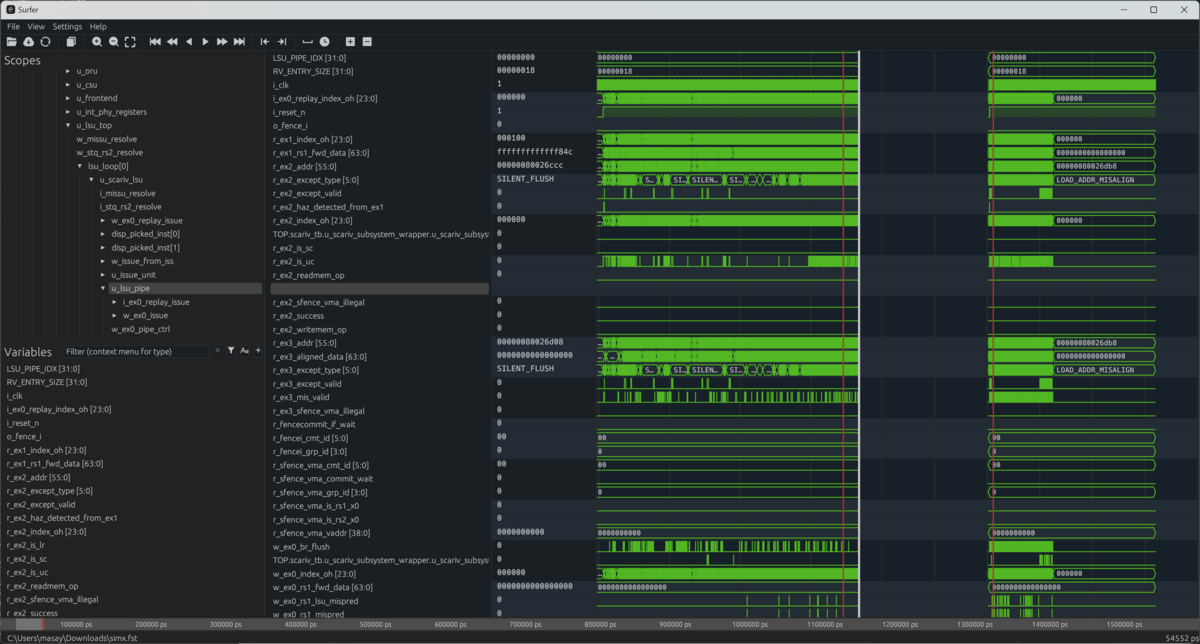

なんか、0x41d8の0xc002000への書き込みの時に例外が発生しているっポイ?

41d4: ffc6f813 and a6,a3,-4

41d8: 01062023 sw a6,0(a2)

41dc: 31c72603 lw a2,796(a4)

41e0: 3205a703 lw a4,800(a1)

41e4: 00e61a63 bne a2,a4,41f8 <uart_write+0x54>

41e8: 12003637 lui a2,0x12003

0x41d8で、ST例外が発生しているようだが、tvalが0になっている。アドレス計算に失敗している?

レジスタの読み出し状況をチェックする必要がある。