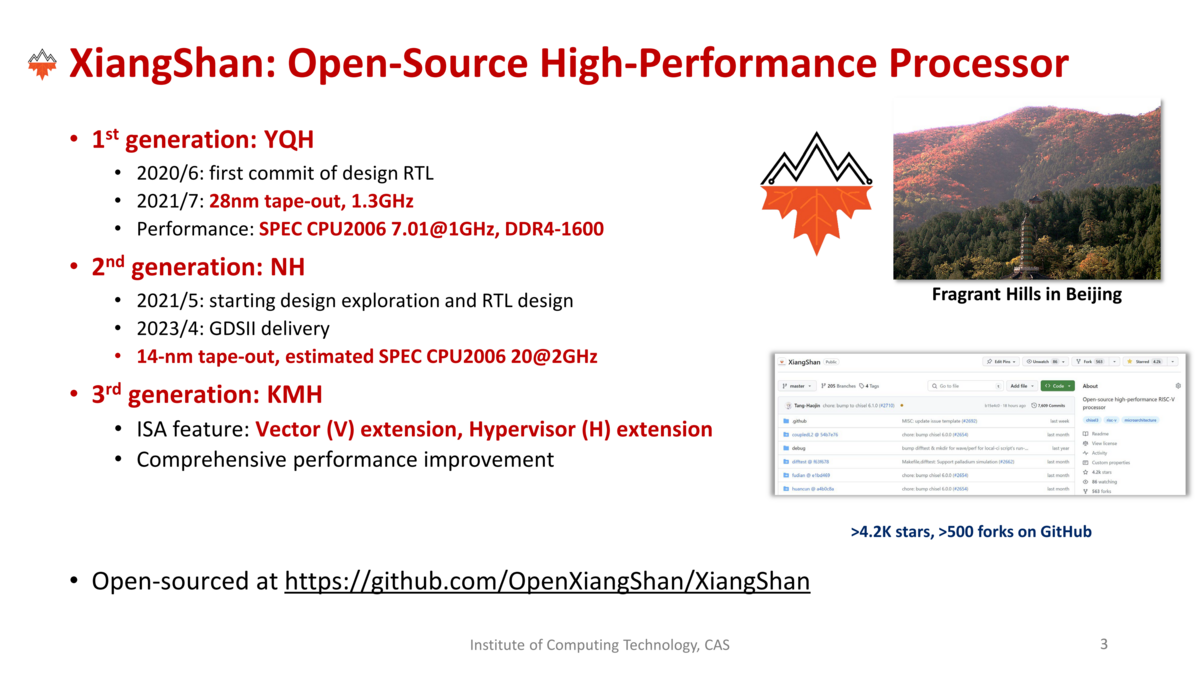

HPCA2024で開催された、RISC-Vのアウト・オブ・オーダCPU XiangShanについての資料が公開されていたので、読んでみることにした。 じっくり読みたいので、1ページずつ要点を抑えていく。

実際のGitHubリポジトリをダウンロードして、いろいろ試してみようと思う。

- Gitリポジトリのダウンロード:

以下で、build/XSTop.vにChiselから生成されたVerilogが生成される。

git clone https://github.com/OpenXiangShan/XiangShan.git --recurse-submodules cd XiangShan make verilog

ちなみに、ドキュメントに書いてある通りの以下のコマンドだと落ちてしまった。

make emu CONFIG=MinimalConfig MFC=1 -j$(nproc)

[warn] intrGenRegs(randomPosition(5)) := intrReg(randomPosition(5)) | UIntToOH(randomPosition(4, 0))

[warn] ^

[warn] There were 63 warning(s) during hardware elaboration.

Exception in thread "main" java.util.NoSuchElementException: NOOP_HOME

at ... ()

...

at logger.Logger$.$anonfun$makeScope$4(Logger.scala:148)

at scala.util.DynamicVariable.withValue(DynamicVariable.scala:59)

at logger.Logger$.makeScope(Logger.scala:146)

at logger.Logger$.makeScope(Logger.scala:133)

at ... ()

at ... (Stack trace trimmed to user code only. Rerun with --full-stacktrace to see the full stack trace)

1 targets failed

xiangshan[chisel].test.runMain subprocess failed

make: *** [Makefile:133: build/rtl/SimTop.v] Error 1

ブランチをkunminghuに変更してみたが、それでもだめだった。

git checkout kunminghu git submodule update --init --recursive make emu CONFIG=MinimalConfig MFC=1 -j$(nproc)

一応、MFC=1だけ(MLIRを使用する)では、ビルドしてVerilogファイルを生成できるようだ。

make MFC=1 -j$(nproc)

もうちょっとマニュアルをまじめに見ながらやってみる。

git clone https://github.com/OpenXiangShan/NEMU.git cd NEMU export NEMU_HOME=${PWD} cd .. git clone https://github.com/OpenXiangShan/nexus-am.git cd nexus-am export AM_HOME=${PWD} cd XiangShan export NOOP_HOME=${PWD} make emu CONFIG=MinimalConfig MFC=1 -j$(nproc)

パッケージのインストールが必要だ:

make[3]: Entering directory '/home/msyksphinz/work/riscv/xiangshan/XiangShan/build/emu-compile'

In file included from /home/msyksphinz/work/riscv/xiangshan/XiangShan/build/chisel_db.cpp:2:

/home/msyksphinz/work/riscv/xiangshan/XiangShan/build/chisel_db.h:12:10: fatal error: sqlite3.h: No such file or directory

12 | #include <sqlite3.h>

| ^~~~~~~~~~~

compilation terminated.

make[3]: *** [VSimTop.mk:94: chisel_db.o] Error 1

make[3]: *** Waiting for unfinished jobs....

In file included from /home/msyksphinz/work/riscv/xiangshan/XiangShan/difftest/src/test/csrc/common/compress.cpp:17:

/home/msyksphinz/work/riscv/xiangshan/XiangShan/difftest/src/test/csrc/common/compress.h:26:10: fatal error: zstd.h: No such file or directory

26 | #include <zstd.h>

| ^~~~~~~~

compilation terminated.

make[3]: *** [VSimTop.mk:104: compress.o] Error 1

In file included from /home/msyksphinz/work/riscv/xiangshan/XiangShan/difftest/src/test/csrc/common/ram.cpp:22:

/home/msyksphinz/work/riscv/xiangshan/XiangShan/difftest/src/test/csrc/common/compress.h:26:10: fatal error: zstd.h: No such file or directory

26 | #include <zstd.h>

| ^~~~~~~~

compilation terminated.

make[3]: *** [VSimTop.mk:124: ram.o] Error 1

make[3]: Leaving directory '/home/msyksphinz/work/riscv/xiangshan/XiangShan/build/emu-compile'

make[2]: *** [verilator.mk:140: build_emu_local] Error 2

make[2]: Leaving directory '/home/msyksphinz/work/riscv/xiangshan/XiangShan/difftest'

make[1]: *** [verilator.mk:144: /home/msyksphinz/work/riscv/xiangshan/XiangShan/build/emu] Error 2

make[1]: Leaving directory '/home/msyksphinz/work/riscv/xiangshan/XiangShan/difftest'

make: *** [Makefile:179: emu] Error 2

sudo apt install libsqlite3-dev libzstd-dev

で、やり直し。すると、うまくいったようだ。なにやらVerilatorのビルドが走り始めた。結構時間がかかるようだ。

Coremarkも試してみる。

The image is /home/msyksphinz/work/riscv/xiangshan/nexus-am/apps/coremark/build/coremark-riscv64-xs.bin Running CoreMark for 10 iterations 2K performance run parameters for coremark. CoreMark Size : 666 Total time (ms) : 21663 Iterations : 10 Compiler version : GCC13.1.0 seedcrc : 0xe9f5 [0]crclist : 0xe714 [0]crcmatrix : 0x1fd7 [0]crcstate : 0x8e3a [0]crcfinal : 0xfcaf Finished in 21663 ms. ================================================== CoreMark Iterations/Sec 461