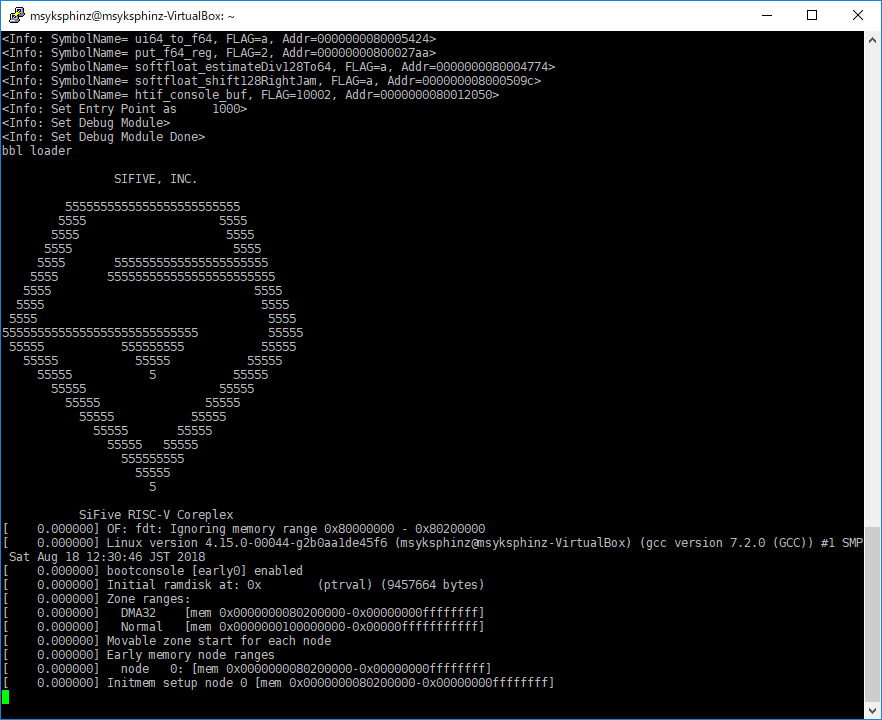

CPU脆弱性についての論文を読んでいると必ずと言っていいほど出てくるIntel SGX(Software Guard Extension)。 なんとなく秘匿データを扱うためのIntelのハードウェア機構なんだろうなと思っていたけど、あまり知ったかぶりをしているのもよくないのでチュートリアルを読んでみることにした。

参考にしたのは、Intel® Software Guard Extensions Tutorial Series だ。ハードウェアの詳細について書いてあるわけではないが、使い方についていろいろ書いてあるので基礎知識を得るのにはよさそう。

長々と書いているが要するに、

- SGXは秘密情報を扱うためにアプリケーション階層内に「飛び地(enclave)」を作成する。この飛び地に秘密情報を格納して管理する。

- enclaveに入れるのは、Intelの専用命令を実行した場合のみだ。新しく追加されたSGX用の専用命令により、コアはSGXの内部のデータにアクセスできるようになる。

- 複数のenclaveがデータをアクセスするために、鍵を管理するための複数の機構が用意されている。

最初は1段落1まとめくらいでメモを取っていたのだが、だんだん翻訳になっていったのでそのまま掲載する。

ただし、あまり深入りせずに基礎知識を手に入れた段階で手を引くつもり。

Intel Software Guard Extension チュートリアル連載

Part-1 Intel SGX Foundation

Intel Software Guard Extensionテクノロジを理解する

ソフトウェアの中で、「パスワード・アカウント番号・秘密鍵・健康状態の記録」などといった秘密にしなければならないデータを扱うときに、Intel SGXの技術を使用すると、これらの情報をアプリケーションの秘密情報として使用することができる。

意図しないアプリケーションからの秘密情報へのアクセスや、権限を持っていないアプリケーションからOSの秘密情報へのアクセスは防がなければならない。アプリケーションは情報の暗号化などの秘密保持技術を使用して、秘密情報をサードパーティのストレージに転送したり、ネットワーク越しにデータの転送を行う。

しかしこれ以外に、コンピュータシステム内でも様々な脆弱性が存在する。あるアプリケーションが扱っている秘密情報を守ろうとしても、マルウェアがより高い権限を持って制限のないアクセスを知ってしまうと、システム上で動作しているすべてのシステムとすべてのアプリケーションの情報が取得されてしまう。洗練されたマルウェアはアプリケーションの保護機構を狙い、暗号カギを抽出して極秘データ自身を直接メモリから取得してしまう。

ソフトウェアによるこれらの攻撃を防ぐために、開発されたのがIntel SGXだ。Intel SGXはCPU命令セットの集合であり、アプリケーションが「飛び地」、つまりアプリケーションのアドレス領域において秘匿性やインテグリティを確保することができる領域を作成する。「飛び地」のコードは特殊命令によって有効化され、WindowsのDynamic Link Library(DLL)ファイルによってロードされる。

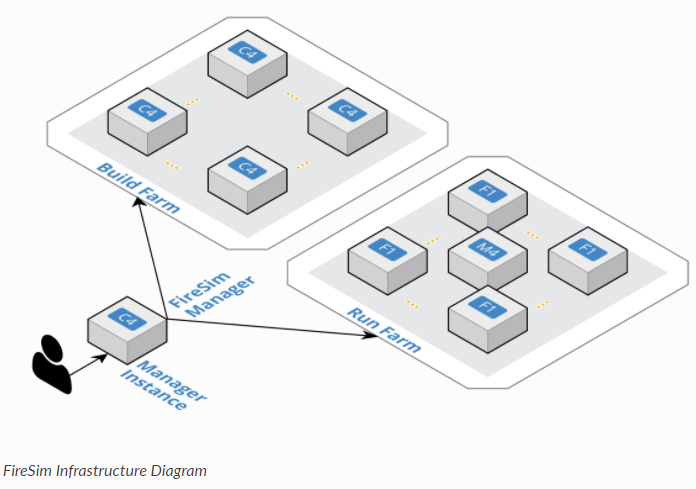

Intel SGXはアプリケーションの境界による攻撃を削減することができる。図1. は、Intel SGXを使用した場合と使用しない場合での攻撃の海面を示している。

Intel Software Guard Extensionテクノロジはどのようにしてデータを守るのか

- 飛び地のメモリ領域は、現在の権限モードとCPUモードに関わらず、飛び地領域の外からアクセスすることはできない。

- Production Enclavesは、ソフトウェア・ハードウェアデバッガを使ってデバッグすることはできない。

- 通常の関数呼び出し・ジャンプ・レジスタ操作によってEnclave領域に入ることはできない。Enclave関数に入るための唯一の方法は、いくつかの保護チェックを実行する新しい命令を実行する以外にない。

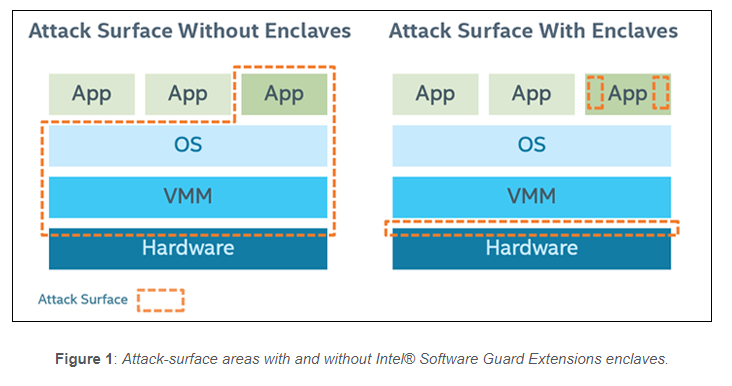

- EnclaveメモリはRelay Protectionを使用した業界標準の暗号化技術を使用して暗号化される。メモリをタッピングしたり、DRAMモジュールを他のシステムに接続すると、暗号化されたデータのみやり取りが行われる(図2. を参照のこと)

- メモリの暗号化鍵は、すべての電源サイクル(例えば、ブート時・スリープやハイバネーション状態からの復帰時)でランダムに変更される。暗号化鍵はCPUに保持されアクセスすることはできない。

- Enclaveにより保護されたデータはEnclaveを共有するコードによってのみアクセスすることができる。

保護メモリの領域はBIOSによって設定され、64MBか128MBである。いくつかのシステムではBIOSセットアップにより他のオプションを提供する場合がある。各Enclaveのフットプリントによって、メモリ中におおよそ5~20個のEnclaveをメモリ中に同時に作成することができる。

Design Consideration

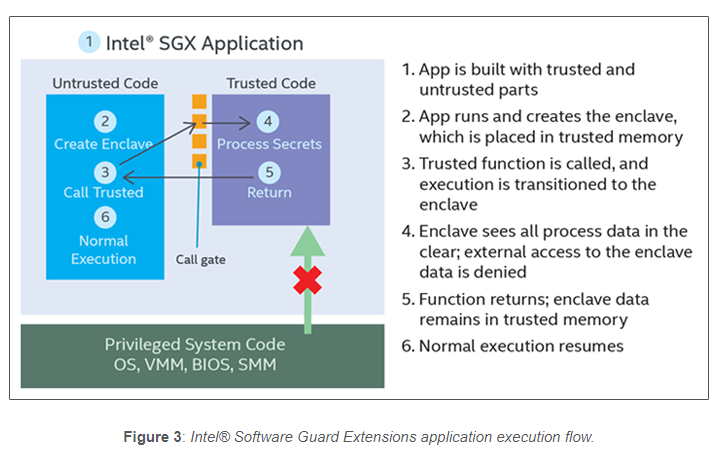

Intel SGXを使用するアプリケーションは、2つのコンポーネントに分割される必要がある(図3. を参照のこと)。

- Trustedコンポーネント Enclaveのこと。Trustedコード中のコードはアプリケーションの秘密情報にアクセスすることができる。アプリケーションは、1つ以上のTrustedコンポーネント・Enclaveを持つことができる。

- Untrusted コンポーネント アプリケーションないのTrustedでない領域のこと。OSやVMMなどはUntrustedコンポーネントであると考えることができる。

Trustedコンポーネントは可能な限り小さくするべきである。保護が必要なデータと、そのデータに対する捜査を行う操作のみをTrustedコンポーネントにすべきである。Enclaveを大きくしてしまい複雑なインタフェースを持たせてしまうとより多くの保護メモリを消費してしまい、また攻撃可能な境界を増やしてしまう。

また、EnclaveはTrustedとUntrustedなコンポーネントのインタフェースを最小限に抑えるべきである。Enclaveが保護されたメモリ領域を飛び出し、Untrustedなコンポーネントを呼び出すとき(これには特殊な命令が必要である)、TrustedとUntrustedの依存性を最小限に抑えることにより、Enclaveが攻撃される可能性を抑えることができる。

Attestation(日本語訳: 証明・証拠)

Intel SGXアーキテクチャでは、Attestationとはプラットフォーム上で特定のEnclaveが構成されたことを示すためのプロセスを指す。2つのAttestationのメカニズムが存在する。

- Local Attestation 同一プラットフォーム上の2つのEnclaveが互いに認証したときにこの状態を指す。

- Remote Attestation Enclaveが、信頼できるリモートプロバイダから認証を得たときにこの状態を指す。

Local Attestation

Local Attestationは、1つのアプリケーションが複数のEnclaveを保持しており、これらが互いに強調して動作しなければならない場合や、2つのアプリケーションがEnclaveを通じて互いにコミュニケーションをとらなければならないときに有用である。互いのEnclaveは、互いが信頼できることを確認するために、互いの検証を行う必要がある。検証が完了すると、互いに保護されたセッションを構築し、ECDH鍵交換を使用してセッション鍵を交換する。このセッション鍵は2つのEnclave間でデータを共有するための暗号化に使用される。

Remote Attestation

Remote Attestationでは、サードパーティのサーバを使用して認証を獲得するのだが、そのためのくおーとを生成するためにIntel SGXソフトウェアとハードウェアを使用する。ソフトウェアにはアプリケーションのEnclaveとQuoting Enclave(QE)、Provisioning Enclave(PvE)が含まれている。QEとPvEはどちらともIntelから提供される。Attestationのハードウェアは、Intel SGXが有効化されたCPUである。ソフトウェアの情報はプラットフォームで単一な非対称鍵と掛け合わされ、信頼されたチャネルを通じてリモートサーバに転送される。リモートサーバが、転送されたEnclaveがIntel SGXが動作可能なプロセッサ上で正常にインスタンスされ実行されていること判断した場合、Enclaveを信頼し、認証されたチャネル上に秘密情報をプロビジョニングできるようになる。

データのシーリング(日本語訳: データの密閉)

データのシーリングは、データを暗号化する処理のことであり、これにより他社に内容を読み取られることなく、秘匿データを保護されていないメモリやストレージ上に配置することができる。データはEnclaveにより読み取られ、アンシール(複合化)することができる。暗号化鍵はオンデマンドに入手することができ、Enclaveの外に漏れることは無い。

データをシーリングするためには2つの方法がある:

- Enclave Identity 特定のEnclaveに対してユニークな鍵を生成する。

- Sealing Identity この方法ではEnclaveのSealing Authorityの一意性をベースにして鍵が生成される。複数のEnclaveでも、同一の署名権限により同一の鍵が生成される。

Enclave Identityによるデータのシーリング

Enclave Identityによりシーリングされたデータは、生成された鍵は特定のEnclaveで一意であり、署名が変わるようなEnclaveの変更により常に新しい鍵が再生成される。この方法を使用すると、古いEnclaveでは新しいEnclaveで作成されたデータにアクセスすることができない。この方式では、アプリケーションが新しくなると、古い鍵は常に使用されないようなケースで使用することができる。

Sealing Identityによるデータのシーリング

Sealing Identityによりシーリングされたデータは、複数のEnclaveが同一の権限を持っている場合に、データを互いにシーリングしたりアンシーリングすることができる。これによりある版のEnclaveが他のEnclaveに移植された場合や、同一ソフトウェアベンダのアプリケーションでデータを共有できるようになる。

もし古いソフトウェアとEnclaveが、新しいソフトウェアでシーリングされたデータにアクセスすることを禁止しなければならない場合、権限をSoftware Version Number(SVN)により管理することができる。Enclaveのバージョンが特定のSVNよりも古い場合、シーリングされたデータを扱うことができない。

本チュートリアルにおけるIntel Software Guard Extensionの使用方法

私たちはIntel SGXの鍵となる3つのコンポーネントについて説明した: enclave, attestation, sealingである。このチュートリアルでは、Intel SGXの搭載されているコアでのenclaveの実装方法について焦点を当てる。最初はattestationとsealingについては触れない。私たちは本チュートリアルを管理できる量に収めたいからだ。

次にやること

本チュートリアルのPart 2では、Intel Software Guard Extensions Tutorial Series: Part 2, アプリケーションデザイン においてパスワード管理アプリケーションに焦点を当て、Intel SGXを使用して構築する方法を示す。デザインの必要なツールや制限、そしてユーザインタフェースについてカバーする。チャンネルはそのまま!

本チュートリアルのすべての文章は、Introducing the Intel® Software Guard Extensions Tutorial Series から見ることができる。