RISC-V トレース機能は、プログラム実行時の挙動を外部へ記録し、デバッグ・性能解析・実行経路再現などを可能とする仕組みである。

本機能は主として、Trace Encoder がトレース情報を生成し、各種 Sink がそれを保存・出力するという構造で成り立っている。

1. Trace Encoder

Trace Encoder はトレースシステムの中心的構成要素であり、HART(CPU コア)からの実行情報を受け取り、トレースメッセージ(パケット)へ変換する役割を担う。

トレースメッセージは バイト列として定義されており、エンコーダ内部では固定幅のトレースワード(通常 1 バイト)にパックされる。

また、Trace Encoder は最低 1 つのシンク、あるいはFunnelに接続されていなければならない。

2. Trace Sink

Trace Encoder が生成したメッセージは Sink によって保存または外部出力される。仕様書では複数の Sink が定義されている。

SRAM Sink

オンチップ RAM にリングバッファ方式でトレースを書き込む仕組みである。

System Memory Sink

システムメモリに DMA 方式で書き込みを行う Sink であり、バッファ満了時には停止またはラップ動作を行うことができる。また、PCIe や USB などを経由してオフチップ出力にも利用可能である。

PIB Sink

エンコーダからのトレースを UART や Manchester, SWT などのプロトコルで外部へ送信する Sink である。

3. ATB Bridge

ATB Bridge は、RISC-V トレースを Arm CoreSight の ATB(Advanced Trace Bus)へ送るためのブリッジである。

Arm と RISC-V が混在する SoC で利用される構成であり、RISC-V 専用システムでは必須ではない。

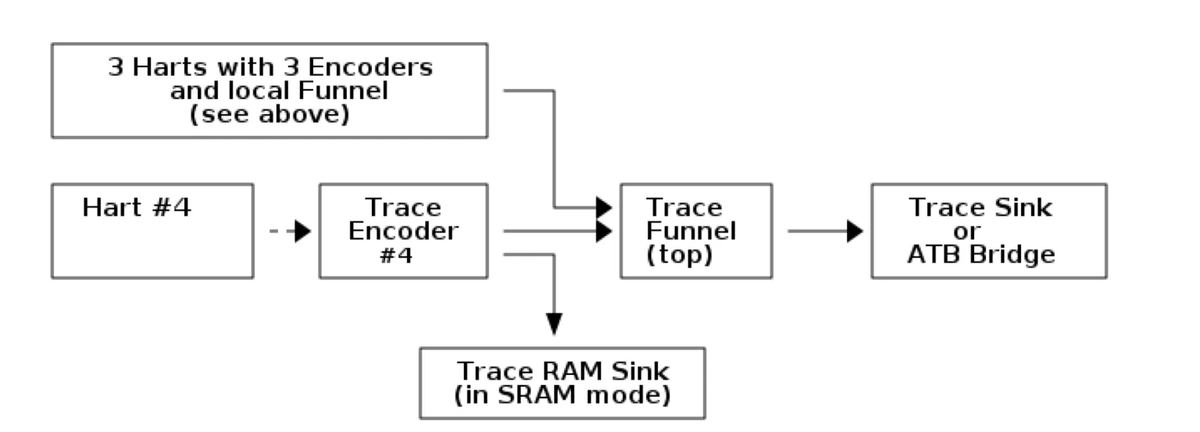

4. Trace Funnel

Trace Funnel は複数の Trace Encoder または他の Funnel からのトレースを 集約し、1 本のトレースストリームにまとめる部品である。

各入力元は固有の Source ID を持つ必要がある。

5. Trace Control Interface

トレース全体の制御は 32bit のレジスタ群を用いて行われる。

各 Trace Component は最大 4 KB のレジスタ空間を持ち、4 KB 境界にアラインして配置される。

また、マルチハート構成では各HARTに専用の Trace Encoder を用意し、生成されるトレースメッセージには HARTID を含める仕組みが定義されている。

トレースに関するコンポーネント

1. Trace Encoder (トレース・エンコーダ)

- HARTからの生トレース情報(命令アドレス等)を N-Traceパケットにエンコードするコンポーネント。

- 各HARTに通常 1 個配置される。

- 最初のステージとして動作する。

2. Trace Funnel (トレース・ファンネル)

- 複数の Trace Encoder からのトレースを 多入力・単一出力でマージするコンポーネント。

- 多HART構成や多層階層構成に対応。

- Funnel 同士を階層的に繋ぐことも可能。

仕様の表では Encoder → Funnel、Funnel → Funnel の接続が許可されている。

3. Trace RAM Sink (RAM シンク)

- トレースデータを メモリバッファ(RAM)へ格納するコンポーネント。

- オンチップ SRAM またはシステムメモリに書き込む構成が可能。

- オフライン解析やデバイス内ログ収集向け。

Trace Encoder → RAM Sink の接続が定義されている。

4. Trace PIB Sink (PIB シンク)

- トレースデータを ピン出力(UART/Manchester/SWT 等のプロトコル)として外部ツールへ送出する。

- SoC 外部のデバッガやトレースツールが受信。

Encoder/Funnel → PIB Sink が許可されている。

5. Trace ATB Bridge (ATB ブリッジ)

- RISC-V トレースを Arm CoreSight の ATB(Advanced Trace Bus) インフラへ橋渡しするコンポーネント。

- 異アーキテクチャ混在システムで使用。

Encoder/Funnel → ATB Bridge の接続が規定されている。

0. コンポーネント共通

各トレース・コンポーネントは以下のレジスタを持つ。

- Control レジスタ(tr??Control)

- Implementation 情報レジスタ(tr??Impl)

tr??Control には tr??Active ビットがあり、0 の間は他レジスタの動作は未定義である。

コンポーネント種別とベースアドレス記号:

| 種別 | type 値 | ベースアドレス記号 |

|---|---|---|

| Trace Encoder | 0x1 | trBaseEncoderN |

| Trace Funnel | 0x8 | trBaseFunnelN |

| Trace RAM Sink | 0x9 | trBaseRamSinkN |

| Trace PIB Sink | 0xA | trBasePibSinkN |

| Trace ATB Bridge | 0xE | trBaseAtbBridgeN |