前回はこちら:msyksphinz.hatenablog.com

UVMのさらなるテストベンチを試行するために、以下のウェブサイトのサンプルを試してみることにした。

このページでは、別ページで作ったSystemVerilogのレジスタコントローラ(レジスタファイルみたいなもの)を検証するためのUVM環境を作り上げていくものになっている。

前回のコードは、よく見たら、uvm_config_db::set()とuvm_config_db::get()の名前がずれていたために動かないのだった。

uvm_config_dbは少しでも間違えると良く分からないままに動かなくなるかな困るな...

tb_top.sv

initial begin // uvm_config_db_options::turn_on_tracing(); uvm_config_db #(virtual reg_if)::set(uvm_root::get(), "*", "reg_vif", vif); run_test(); $finish; end

test.sv

virtual function void build_phase(uvm_phase phase); super.build_phase(phase); e0 = env::type_id::create("e0", this); if (!uvm_config_db #(virtual reg_if)::get(this, "", "reg_if", vif)) `uvm_fatal("TEST", "Did not get vif") uvm_config_db #(virtual reg_if)::set(this, "e0.a0.*", "reg_vif", vif); endfunction // build_phase

virtual function void build_phase(uvm_phase phase); super.build_phase(phase); e0 = env::type_id::create("e0", this); if (!uvm_config_db #(virtual reg_if)::get(this, "", "reg_vif", vif)) // reg_if --> reg_vifに変更 `uvm_fatal("TEST", "Did not get vif") uvm_config_db #(virtual reg_if)::set(this, "e0.a0.*", "reg_vif", vif); endfunction // build_phase

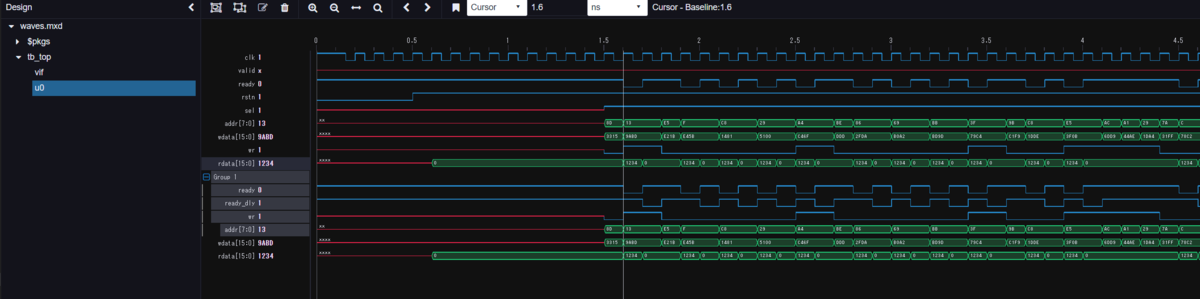

これで、一応動作するようになった。