RISC-VにおけるRVWMOのメモリモデルについて、仕様書を読み直すことにした。

もうちょっと詳しく、RISC-V仕様書のAppendxx A. RVWMOの節を読み解いていくことにした。

A.4 メインメモリを超えて

RVWMOは、現時点では、FENCE.I、SFENCE.VMA、I/Oフェンス、およびPMAs(物理メモリ属性)の振る舞いを形式的に記述しようとはしていない。

これらの振る舞いは、将来の形式化によって記述される予定である。

その間、FENCE.Iの振る舞いは第3章で、SFENCE.VMAの振る舞いはRISC-V命令セット特権アーキテクチャマニュアルで記述されており、I/OフェンスおよびPMAsの効果については以下で説明されている。

A.4.1. コヒーレンス

RISC-V特権ISAは物理メモリ属性(PMAs)を定義している。 これらの属性は、アドレス空間の部分がコヒーレンシがあるか、キャッシュ可能かどうかを含め、様々な特性を指定します。以下に、各PMAがメモリモデルにどのように関連するかについての詳細を簡単に説明します:

- メインメモリ対I/OとI/Oメモリ順序PMAs:メインメモリ領域に適用されるメモリモデル。I/Oの順序については後述される。

- サポートされるアクセスタイプと原子性PMAs:各領域がサポートするプリミティブの上に、たんにメモリモデルが適用される。

- キャッシュ可能性PMAs:一般的にキャッシュ可能性PMAsはメモリモデルに影響を与えない。キャッシュ不可能領域はキャッシュ可能領域よりも制限的な振る舞いをする場合があるが、許可される振る舞いのセットは変わらない。ただし、プラットフォーム固有またはデバイス固有のキャッシュ可能性設定は異なる場合がある。

- コヒーレンスPMAs:PMAsで非コヒーレンスとマークされたメモリ領域のメモリコヒーレンシモデルは、現在プラットフォーム固有および/またはデバイス固有である。非コヒーレンスメモリでは、ロード値の公理、原子性の公理、および進行の公理がすべて破られる可能性がある。ただし、コヒーレントのあるメモリはハードウェアキャッシュ・コヒーレンシ・プロトコルを必要としない。

- 冪等性(Idempotency)PMAs:冪等性PMAsは、ロードおよび/またはストアが副作用を持つ可能性があるメモリ領域を指定するために使用され、これはマイクロアーキテクチャによって、例えばプリフェッチが合法かどうかを判断するために使用される。この区別はメモリモデルに影響しない。

A.4.2 I/O Ordering

セクションA.4.2では、I/O(入出力)の順序付けについて説明している。

I/Oにおいて、ロード値の公理と原子性の公理は一般に適用されない。

これは、読み取りと書き込みがデバイス固有の副作用を持つ可能性があり、最近のストアによって「書き込まれた」値以外の値を返すことがあるためである。

それでも、I/Oメモリへのアクセスに対しては、次のようなPreserved Program Orderの規則が一般に適用される。

もしaがプログラム順序でbの前にある場合、そして以下の一つ以上が当てはまる場合、メモリアクセスaはグローバルメモリ順序でメモリアクセスbの前に実行される:

aがPreserved Program Orderでbの前にあり、AcquireとReleaseの順序付けAnnotationはメモリ操作からメモリ操作へ、及びI/O操作からI/O操作へ適用されますが、メモリ操作からI/Oへ、またはその逆へは適用されない。- aとbはI/O領域内で重複するアドレスへのアクセスである。

- aとbは同じ強く順序付けられたI/O領域へのアクセスである。

- aとbはI/O領域へのアクセスであり、aまたはbによってアクセスされたI/O領域に関連付けられたチャネルがチャネル1である。

- aとbは同じチャネル(チャネル0を除く)に関連付けられたI/O領域へのアクセスである。

FENCE命令は、その前身と後継のセットにおいて、メインメモリ操作とI/O操作を区別する。

I/O操作とメインメモリ操作の間の順序を強制するために、コードはPI、PO、SI、SO、加えてPR、PW、SR、SWを含むFENCEを使用する必要がある。

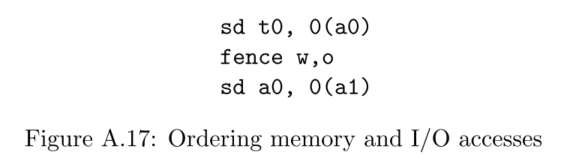

たとえば、メインメモリへの書き込みとデバイスレジスタへのI/O書き込みの間の順序を強制するためには、FENCE W,Oまたはそれ以上の強さが必要である。

フェンスが実際に使用される場合、実装はデバイスがMMIO信号を受信した直後にメモリにアクセスしようとする可能性があると想定し、そのデバイスによるメモリへの後続のメモリアクセスは、そのMMIO操作の前に順序付けられたすべてのアクセスの効果を観察しなければならない。

RISC-Vは、I/O(通常のメインメモリとは対照的に)に関連して、「順序付け」フェンスと「完了」フェンスの別個の概念を特に区別しない。

代わりに、この区別はFENCEビットの異なる使用から単純に推測される。

RISC-V Unixプラットフォーム仕様に準拠する実装では、I/OデバイスとDMA操作は、メモリに対してコヒーレントを持ってアクセスし、強く順序付けられたI/Oチャネルを介して行う必要がある。 従って、外部デバイスによって同時にアクセスされる通常のメインメモリ領域へのアクセスも、標準の同期メカニズムを使用できる。 Unixプラットフォーム仕様に準拠していない実装や、デバイスが一貫性を持ってメモリにアクセスしない場合は、コヒーレントを強制するために現在はプラットフォーム固有またはデバイス固有のメカニズムを使用する必要があります。