ずっと試してみたかった、Tenstorrentが公開したRISC-V検証パタンである riscv_arch_tests を試してみることにした。

自作CPUに適用して、さらなるバグが発見されることを期待している。

とりあえずpkを使わなくても、メモリ領域を拡張することで何とかなりそうな気がしてきた。

spike -l -m0x80000000:65536,0x726000:4096 ../tests/riscv_arch_tests/riscv_tests/rv_i/rvi_compute_register_register/rvi_compute_register_register_1

メモリ領域を定義して、エラーで指定されたメモリ領域を0x726000を定義する。 いちおうこれでテストパタンが動き出すようになった。

core 0: 0x0000000000001000 (0x00000297) auipc t0, 0x0 core 0: 0x0000000000001004 (0x02028593) addi a1, t0, 32 core 0: 0x0000000000001008 (0xf1402573) csrr a0, mhartid core 0: 0x000000000000100c (0x0182b283) ld t0, 24(t0) core 0: 0x0000000000001010 (0x00028067) jr t0 core 0: >>>> __section_text core 0: 0x0000000080000000 (0x00000013) nop core 0: >>>> init core 0: 0x0000000080000004 (0x00000093) li ra, 0 core 0: 0x0000000080000008 (0x00000113) li sp, 0 core 0: 0x000000008000000c (0x00000193) li gp, 0 core 0: 0x0000000080000010 (0x00000213) li tp, 0 core 0: 0x0000000080000014 (0x00000293) li t0, 0 core 0: 0x0000000080000018 (0x00000313) li t1, 0 core 0: 0x000000008000001c (0x00000393) li t2, 0 core 0: 0x0000000080000020 (0x00000413) li s0, 0 core 0: 0x0000000080000024 (0x00000493) li s1, 0 core 0: 0x0000000080000028 (0x00000513) li a0, 0

早速自作CPUで動かしてみる。 MISAの設定が違うのかな?

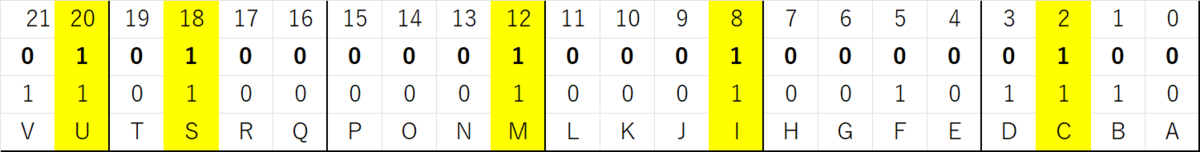

2223 : 41 : PC=[0000000080000090] (M,07,01) 12e08093 addi ra, ra, 302 GPR[01](28) <= 800000000034112e 2229 : RTL(8,1) Exception Cause = CSR Update Flush(27) PC=000080000094, Inst=30109073, csrw misa, ra 2229 : 42 : PC=[0000000080000094] (M,08,01) 30109073 csrw misa, ra 2249 : RTL(13,1) Exception Cause = CSR Update Flush(27) PC=000080000098, Inst=301020f3, csrr ra, misa 2249 : 43 : PC=[0000000080000098] (M,13,01) 301020f3 csrr ra, misa ========================================== Wrong GPR[01](37): RTL = 800000000034112e, ISS = 8000000000141104 ==========================================

MISAとしては、RV64IMCが正解らしい。MISAの設定がちょっと問題だ。