必要に迫られてRISC-VのアウトオブオーダプロセッサBOOMのMSHR周りの動作を見ていたのだが、どうにもChiselは柔軟に書けすぎて何が起きているのかよく掴めない。

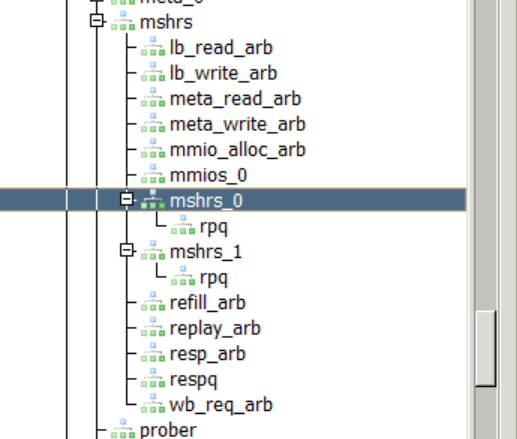

分かるのはMSHRは2エントリ用意されているということ。これで間に合う?

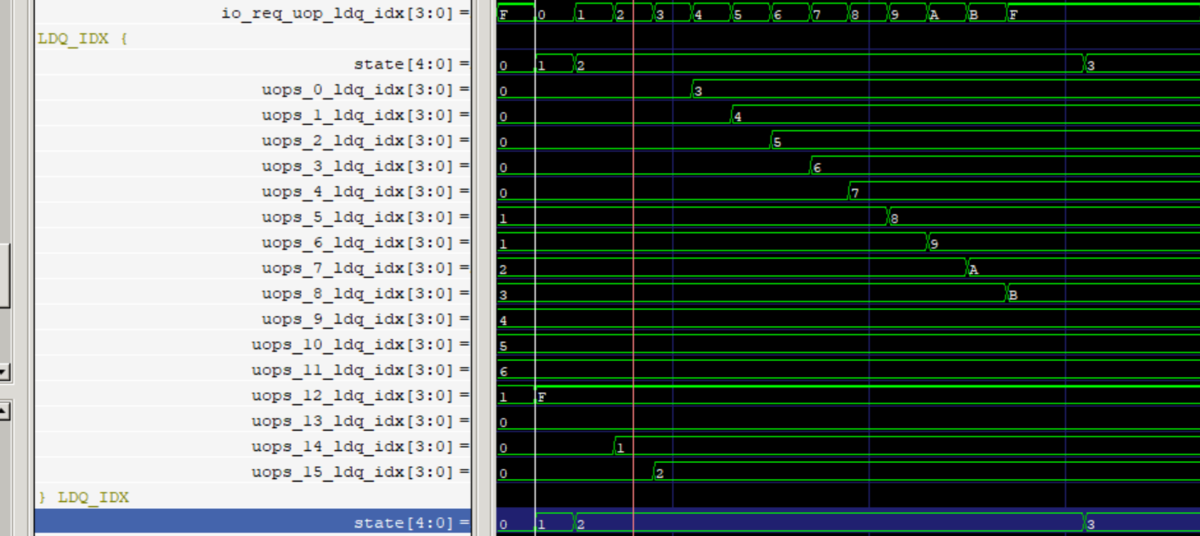

あと、MSHRはミスが発生した同様なキャッシュラインのLDQのインデックスを記憶している。以下のような感じ。

RPQというのは何だろう?Refill Pending Queue?

ここから先、LDQのインデックスを持っているが、これは活用しているのか、していないのか? どういうポリシでLDQがウェイクアップしているのか、まだよくわからない。

// Handle the response when (io.dmem.resp(w).valid) { when (io.dmem.resp(w).bits.uop.uses_ldq) { assert(!io.dmem.resp(w).bits.is_hella) val ldq_idx = io.dmem.resp(w).bits.uop.ldq_idx val send_iresp = ldq(ldq_idx).bits.uop.dst_rtype === RT_FIX val send_fresp = ldq(ldq_idx).bits.uop.dst_rtype === RT_FLT io.core.exe(w).iresp.bits.uop := ldq(ldq_idx).bits.uop io.core.exe(w).fresp.bits.uop := ldq(ldq_idx).bits.uop io.core.exe(w).iresp.valid := send_iresp io.core.exe(w).iresp.bits.data := io.dmem.resp(w).bits.data io.core.exe(w).fresp.valid := send_fresp io.core.exe(w).fresp.bits.data := io.dmem.resp(w).bits.data assert(send_iresp ^ send_fresp) dmem_resp_fired(w) := true.B ldq(ldq_idx).bits.succeeded := io.core.exe(w).iresp.valid || io.core.exe(w).fresp.valid ldq(ldq_idx).bits.debug_wb_data := io.dmem.resp(w).bits.data }