ちょっと読んでいる論文のメモその2:

4. SRVメモリ曖昧さ回避アーキテクチャ

A. 用語解説

- 水平依存:従来のステートメント間のデータ依存

- 垂直依存:レーン間の依存

リスト3は、2つのベクトルロード命令と1つのベクトルストア命令を持つSRV領域である。

- 命令A : x配列の連続した16個の要素をデータに書き込む

- 命令B:x配列の同じ要素からデータを読み出す (垂直依存性)

- 命令C:x配列の連続した16個の要素からデータをロードする。v_storebと依存関係が存在している(垂直依存)。

- このように、命令Aのレーン9は命令Cのレーン1と水平方向に依存関係が存在している。

srv_start v_storeb v0, x[i:i+15] // 命令A ... v_loadb v1, x[i:i+15] // 命令B ... v_loadb v2, x[i+8:i+23] // 命令C srv_end

従来の水平方向の依存性に加えて、特定のベクトルアーキテクチャのベクトル長に合わせたアドレス空間をアドレスアラインメント領域と定義する。アライメント領域の開始アドレスをアドレスアライメントベースと読んでいる。

B. 垂直曖昧性解消機構

LSUには図2で示したVertical Disambiguation Logicを含んでいる。発行時に計算されるSAQとLQのビットベクタで、アドレスアラインメントベースに対してアクセスされるバイトに対応する。つまりバイトアクセスをビットベクタで示したものとなる。

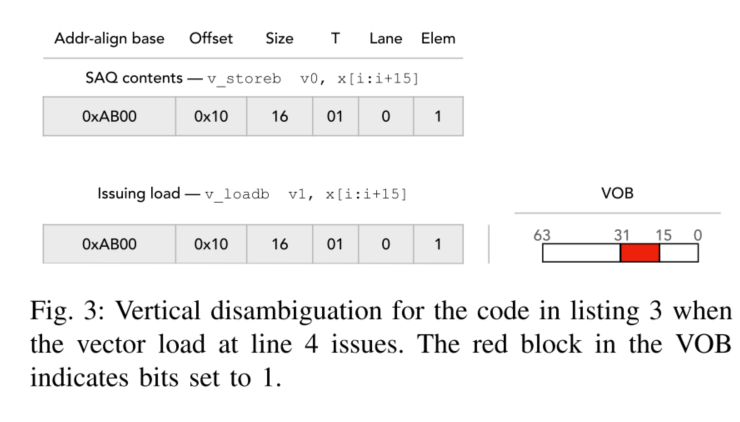

図3はリスト3のコード例である。各命令のアドレスアライメントベースが0xAB00で、データが16バイトのオフセットであるとすると、各命令は1バイト毎にアクセスを行うので、Elemフィールドは1、サイズは16となる。

命令Bが発行されると、SAQが参照され、命令Aを含むエントリでマッチングが発生する。量命令においてバイトアクセスビットベクタは同じなので、VOBビットベクタはオーバラップするメモリアドレスのすべてのビットに設定される。このビットベクタを参照することにより、ロードするベータはすべてストアに書き込まれ、ストア命令(命令A)からフォワーディング可能であるということを示している。

詳細には、ロード命令が発行されるとSAQの一致する各行とバイトアクセスビットのANDが行われ、結果はVOBビットベクタに書き込まれる。

C. 水平曖昧性解消機構

SRVでは、垂直曖昧性解消論理に加えて、水平曖昧性解消論理を追加している。図2のHorizontal Disambiguation Logicがそれに相当し、水平方向のメモリ依存性違反を特定するためのビットベクタ(Horizontal Violation Bit Vector)と、発行したロードストアに重なるバイトを判定するビットベクタ(HOB Bit Vector)から構成されている。

命令Aと命令Cに対する依存性を考える。命令Cが発行されると、VOBビットベクタによりアドレスアライメントベースからのオフセットを考慮したビットが設定される。しかし、Cのアドレスアライメントオフセットはそれよりも大きいため、後続のレーンにバイトを書き込むことによるメモリ依存性違反が発生する。HOBのビット24以降に設定される水平依存ベクタにより設定される。

srv_start v_storeb v0, x[i:i+15] // 命令A ... v_loadb v1, x[i:i+15] // 命令B ... v_loadb v2, x[i+8:i+23] // 命令C srv_end

D. 実行例

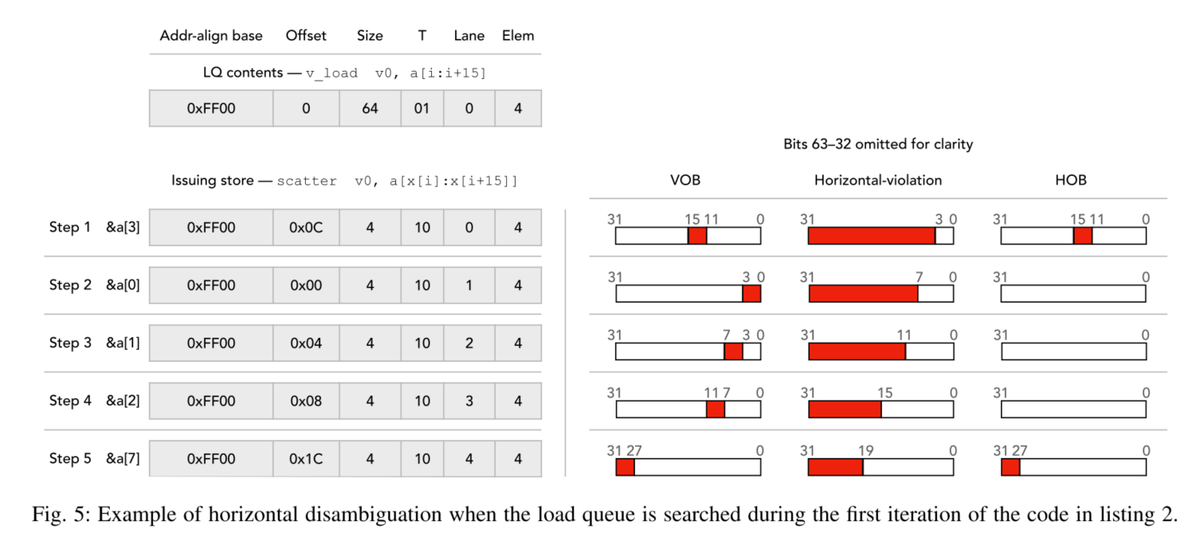

リスト2を用いて、水平RAW違反検出の実用例を示します。ここでは、アドレスアライメント領域が64バイトのLSUで、配列aがアドレス0xFF00に配置されていると仮定しています。図5に最初の実行を示す。先頭のLQエントリにvロード命令に関する情報が記録されている。

リスト2を用いて、水平RAW違反検出の例を示す。

- アドレスアライメント領域は64バイト

- 配列aがアドレス0xFF00に配置されると仮定する。

Loop: srv_start v_load v0, a[i:i+15] v_add v0, 2 scatter v0, a[x[i]:x[i+15]] srv_end inc i, 16 comp i, N bne Loop

scatter命令が16個の異なるストアに分割される。scatter命令が配列aの3番目に書き込むとき、そのアドレスとLQとロードエントリを比較する。この時にアドレスアライメントベースで一致し、アドレスが重複していることを示す。アドレスの被っている12から15バイト目のVOBが設定される。水平曖昧性解消論理は、現在のscatter命令のレーンよりも古いレーンにしか興味が無いので、HOB Violation論理の、最初の4ビット以外のすべてが1に設定される。

scatterはステップ2において、a配列の0番目の要素に書き込む部分から始まる。ベクトルロードのアドレスアライメントベースにマッチするので最初の4ビットが1に設定される。そして、レーン2以降の依存関係に興味があるので8ビット目以降のすべてのHOB violationのビットが設定される。結果的に、VOBとHOB violationのANDによりHOBベクトルは0となり、依存性違反は発生しないことになる。