最近は色々あってCPUのストアバッファについて考えている。 ストアバッファは簡単に言えばコミット済みのストア命令を、STQ(Store Queue)から分離しL1Dキャッシュもしくは外部へ書き込むまでの生存管理を行うものだ。 STQによるLSUパイプライン実行とL1Dへの書き込み処理を分離することで、効率よく動作を管理できるようになる。

ストアバッファについては以下の文章が参考になる。

で、自分でいろいろ考えながら自作CPUのために仕様を書いてみた。以下は備忘録。

ストアバッファ

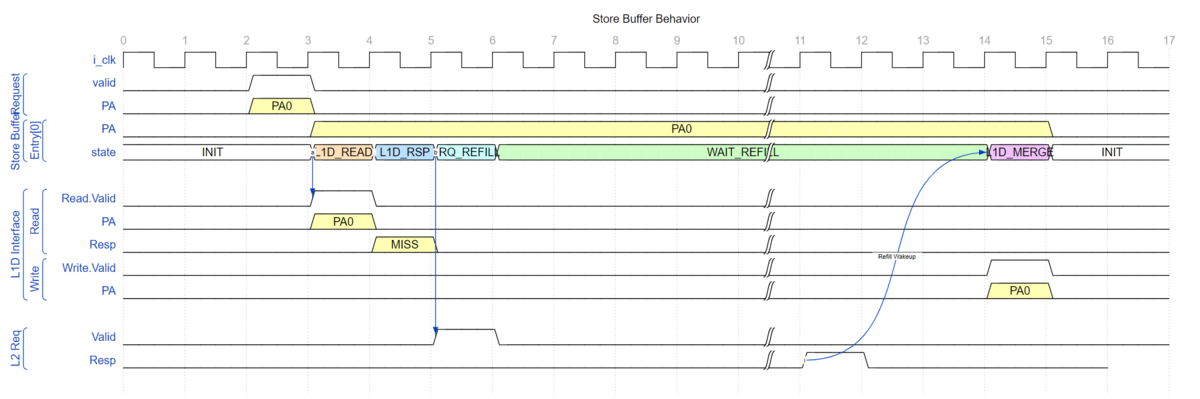

コミットされたストア命令はデータをL1Dに書き込みますが、その前にアドレスとデータの情報はストアバッファに移されます。 ストアバッファはコミットされたストア命令が、L1Dキャッシュに書き込まれるまでの状態を管理します。 ストアバッファは XLEN * 2 ビット幅のデータを管理することができ、隣接する複数のデータを管理することができます。

コミット処理により複数のストア命令がコミット状態になった時、コミット対象の先頭となる命令に対して、 連続する後続のコミット状態の命令も同じストアバッファの管理アドレス範囲に存在している場合、 その複数の命令はマージされてストアバッファに格納されます。

- ストア対象となるアドレスがL1Dに存在しているかどうかをチェックする

- 存在する場合はL1Dに書き込みを行う

- 存在していない場合はLoad L1D Requester(LRQ)に対して当該キャッシュラインのロード要求を行う

- ストアバッファは後続のコミット済みストア命令が同じキャッシュラインに書き込みを行う場合、それを検出してマージを行います。

- マージされたデータは、一緒にL1Dに書き込まれます。

ストアバッファは複数のエントリを持ち、それぞれのエントリは以下のように動作します。

- サイクル1. L1Dキャッシュに対して当該物理アドレスの読み込み処理を行う。2. へ移動する

- サイクル2. L1Dキャッシュに存在していれば(Hit)、3. へ移動する。そうでなければ4.へ移動する

- サイクル3. L1Dキャッシュへの書き込みを行う。処理を終了する

- サイクル3. L1Dキャッシュに存在していない場合、L1D LRQ(Load Requester)にロード要求を発行する。5. へ移動する

- サイクルN. Load Requesterからデータのロード通知を受けると、L1Dキャッシュに対してロードデータのマージリクエストを通知する。処理を終了する