SonicBOOMのロードユースについて調査したい。キャッシュヒットした場合、ロード命令からその次の依存命令まで何サイクル掛かるのか。

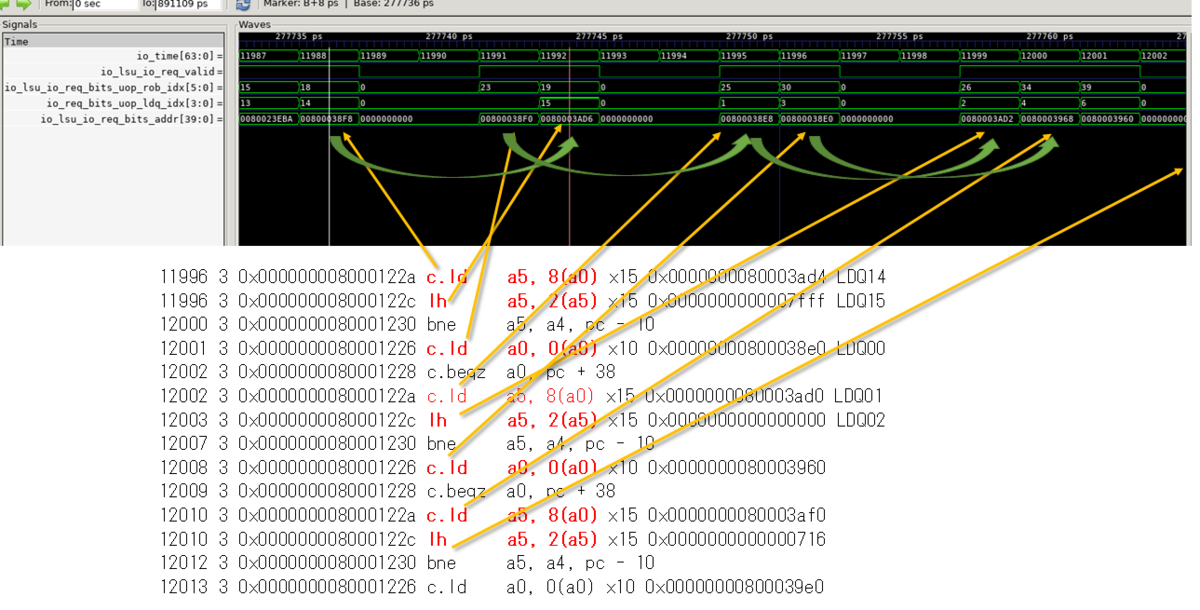

CoremarkのPointer Chase部分についてサイクル数を確認している。当該部分はここになる。

11996 3 0x000000008000122a c.ld a5, 8(a0) x15 0x0000000080003ad4

11996 3 0x000000008000122c lh a5, 2(a5) x15 0x0000000000007fff

12000 3 0x0000000080001230 bne a5, a4, pc - 10

12001 3 0x0000000080001226 c.ld a0, 0(a0) x10 0x00000000800038e0

12002 3 0x0000000080001228 c.beqz a0, pc + 38

12002 3 0x000000008000122a c.ld a5, 8(a0) x15 0x0000000080003ad0

12003 3 0x000000008000122c lh a5, 2(a5) x15 0x0000000000000000

12007 3 0x0000000080001230 bne a5, a4, pc - 10

12008 3 0x0000000080001226 c.ld a0, 0(a0) x10 0x0000000080003960

12009 3 0x0000000080001228 c.beqz a0, pc + 38

12010 3 0x000000008000122a c.ld a5, 8(a0) x15 0x0000000080003af0

12010 3 0x000000008000122c lh a5, 2(a5) x15 0x0000000000000716

12012 3 0x0000000080001230 bne a5, a4, pc - 10

12013 3 0x0000000080001226 c.ld a0, 0(a0) x10 0x00000000800039e0

12014 3 0x0000000080001228 c.beqz a0, pc + 38

12014 3 0x000000008000122a c.ld a5, 8(a0) x15 0x0000000080003b10

12015 3 0x000000008000122c lh a5, 2(a5) x15 0x000000000000070e

12017 3 0x0000000080001230 bne a5, a4, pc - 10

12018 3 0x0000000080001226 c.ld a0, 0(a0) x10 0x0000000080003a60

12019 3 0x0000000080001228 c.beqz a0, pc + 38

12020 3 0x000000008000122a c.ld a5, 8(a0) x15 0x0000000080003b30

12020 3 0x000000008000122c lh a5, 2(a5) x15 0x0000000000000706

12022 3 0x0000000080001230 bne a5, a4, pc - 10

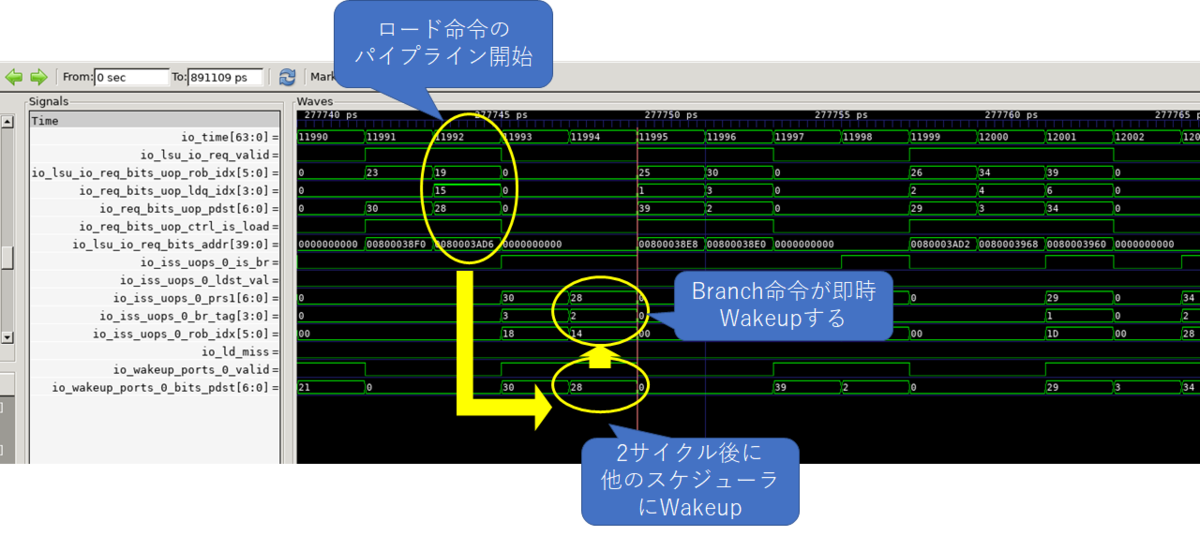

ここのLSUの波形を確認した。リクエストの依存関係は以下のようになっている。

ここから分かることは、それぞれのループにおいて分岐予測を使用して可能な限りロード命令を先出ししているということ。

そして、ロード命令はパイプライン発行後の2サイクルでWakeup信号を他スケジューラに送出する(おそらくL1Dミス/TLBミスすると1サイクル後にld_missがWakeupする)し、

それを受け取った他スケジューラは即時パイプラインへ投入される。