「RISC-V」という言葉が徐々にエンジニア界隈に普及し始め、技術界隈のニュースサイトだけでなく、一般的なニュースを扱うような新聞社の記事でも見かけるようになってきました。例えば以下のような記事です。

半導体エンジニアではない人がこのような記事を書く場合、「設計IP」について正しい知識を持っておかないと、少しおかしなことになってしまいます。しかしこれは記事を書いている記者だけを責めることは出来ません。半導体設計業界はソフトウェア開発業界に比べて小さな業界で、プレーヤの数も少なく、ネット上にあまり情報も出てきません。時事ネタを速攻で記事に起こさないといけない新聞記者が「IPってなんだっけ?」「リスクファイブってなんぞや?」ということをいちいち厳密に調べてられない、ということも理解できます。

そこで、非エンジニア(というか非半導体産業の方)でも理解できるように、RISC-VやARMを中心とする「CPU設計とIP」の関係ということについて可能な限り説明してみたいと思います。この記事は半導体のことを熟知している方のためではなく、非半導体産業の方や、情報処理技術界隈に詳しくない方のためのものです。

「ARM」とは結局何なのか?

現在、世の中には「ARMコア」を採用したチップが大量に溢れています。身近なところではRaspberry-Piや、その他隠れたIoT機器などにも「ARMコア」というものが採用されています。

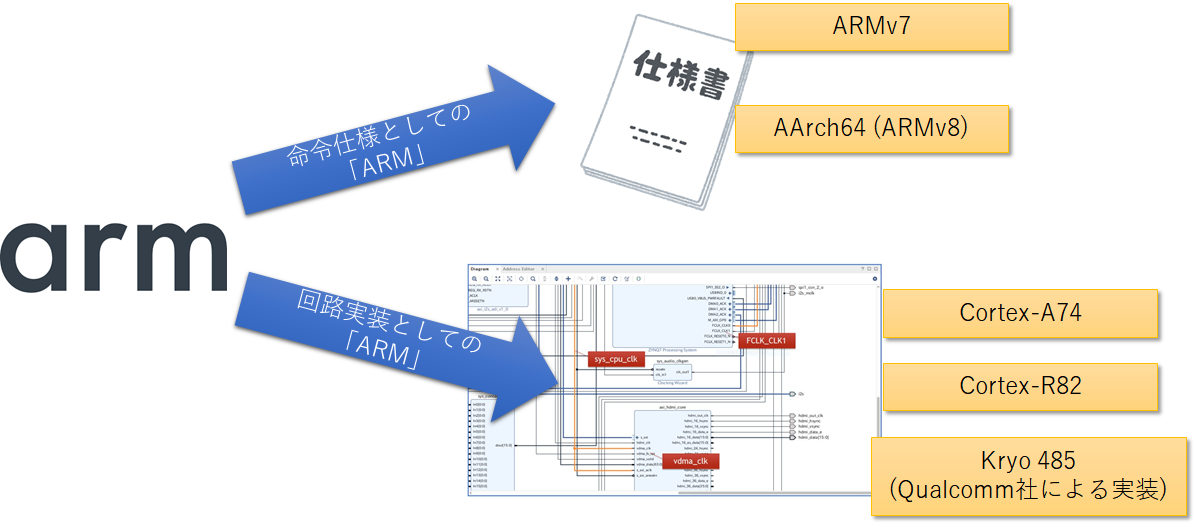

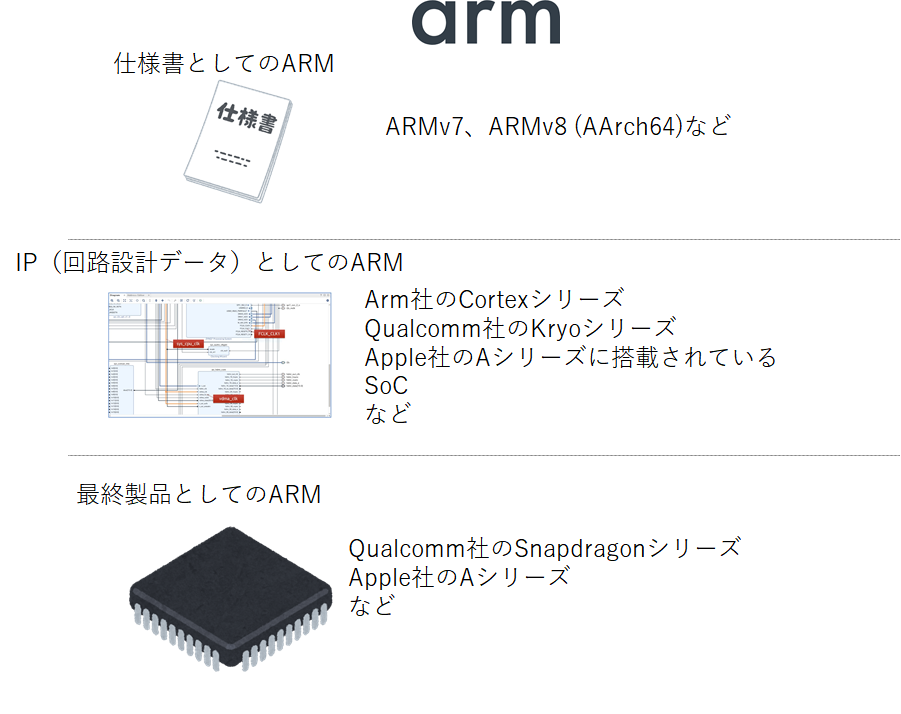

ARMコアは、Arm社が開発し販売しているCPUコアです(本記事では、会社として「Arm社」、コアとして「ARM」という用語を使います)。より具体的にいうと、この「ARM」という言葉には2つの側面があります。

- 命令仕様としての「ARMアーキテクチャ」

- 命令仕様に基づいた回路設計としての「ARMコア」

具体的に言ってしまえば、「命令仕様としてのARM」は仕様書なので「紙に書かれた文書」と考えてもらっても差し支えありません。これは一般的に「ARMアーキテクチャ」や「AArch64(前述のARMは32ビット仕様なのに対し、これを64ビット仕様に拡張したもの)」などと言います。

一方で、回路設計データとしての「ARM」は、上記の仕様書としてのARMを実際の回路として実装したものになります。Arm社が開発したARMコアは有名なものに「Cortex」シリーズがあります。「Cortex-A」「Cortex-R」「Cortex-M」といったものがあります。

このように、回路設計データと命令仕様を分離することで、様々なARMコアが登場します。「Cortex-A73」と「Cortex-A72」はどちらともARMの命令セット「AArch64(=ARMv8)」を採用しており、逆に言えば、一度Cortex-A72用に書いたソフトウェアは特に何の変更も必要なくCortex-A73で動かすことができます。

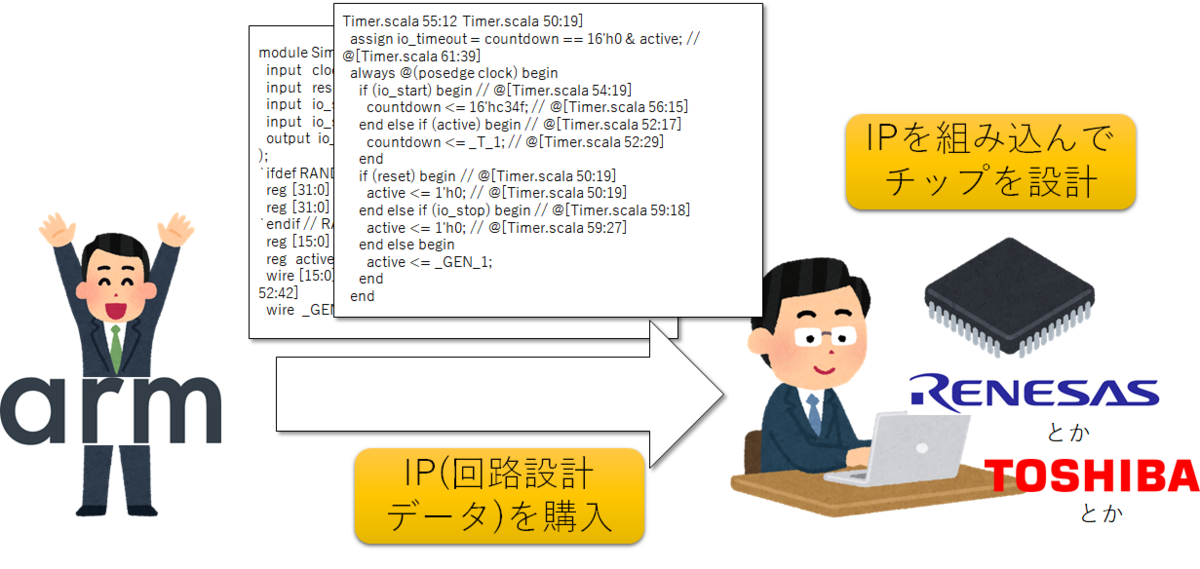

ARM社のビジネスモデルは、自社で開発したCortexシリーズのCPUコア設計データを他社に買ってもらい、ライセンス料を払って儲ける仕組みです。この「回路設計データ」のことを「IP(intellectual property)」と呼ばれ、実体は回路情報の含まれるデジタルデータです。実体はなく、データとして提供されます。

「IP」という言葉は半導体産業では非常に一般的に使用される用語です。しかしこの用語はあいまいで、"Intellectual Property"(知的財産)ってどういうことよ?と思われると思います。私も正直良く分かりません1。とにかく、回路設計データのことを、IPと呼んでいるのです。

世の中に出ているARMコアは、このようにARM社から買ってきた回路情報データを自社のチップ上に実装して、製品として売り出しているものになります。一方でQualcomm社などの複数社は、ARM仕様書に基づき自分で一からARMコアを実装できるライセンスを購入しており2、SnapdragonシリーズなどはQualcomm自身によって開発されたチップであり、Snapdragonの内部にはKryoと呼ばれるQualcomm社が独自に開発したARMコアが搭載されています。AppleのAシリーズも同様です。

「RISC-V」は「命令仕様としてのARM」と立場的に同等のもの

RISC-Vの話に立ち戻ります。ここではっきりさせておかなければならないのは、「RISC-V」は「命令仕様:命令セットアーキテクチャ:ISA」である、ということです。つまり、前述した「命令仕様としてのARM」と立場的には同じものです。そこには紙ペラしかなく、具体的な回路設計情報は含まれていません。

RISC-V Foundationのウェブサイトを見てみましょう。公開されているのはPDFファイルに変換された仕様書のみで、回路設計データは存在していません。この仕様書を管理しているのが「RISC-V Foundation」という非営利団体です。このRISC-V Foundationには大手半導体メーカーなども加入していますが、基本的に仕様の管理はこの非営利団体によって行われています。ARMの仕様はArm一社によって管理されていますが、RISC-Vは様々な組織や人物が使用の策定に加わっています。そこが大きな違いと言えるでしょう。

そして、このRISC-Vの仕様に基づいて様々な企業が「RISC-V CPUコア」の開発に取り組んでいます。RISC-Vの初期仕様の開発に携わった人々が立ち上げたベンチャー「SiFive社」、「Andes Technology」、日本だとNSITEXE社がRISC-V CPUコアの開発を行っています。これらのIPコアは、ARMで言うCortexシリーズと立場的に同等なものです。

「RISC-V」は「IP」ではない

「RISC-V」はあくまでも「命令セットアーキテクチャ(仕様)」であり、「実際の回路設計データ」ではないことははっきりしておかなければなりません。

「RISC-V」がフリーでオープンとはどういうことなのか?

では、RISC-Vが「フリーでオープンである」とはどういうことなのか、ここでもう一度確認しておく必要があります。RISC-Vが設計IPのことを示すわけではないため、設計IPがフリーであるということではないということは自明です。RISC-Vがフリーであるというのは、RISC-V ISAに対応したCPUの開発やソフトウェアエコシステムの開発を、RISC-Vに対してライセンス料を支払わずに行うことができることを意味します。

上述したように、ARMアーキテクチャを使用してCPUを開発するためには「アーキテクチャライセンス」という非常に高額なライセンス料をArm社に支払う必要があります。私は正式にArm社からライセンスを購入したことが無いので分かりませんが、一般に数億円であると言われています。このライセンス料が、RISC-Vの場合には不要となります。

また、「ISAがオープンソース」であるということについては、私の理解では「仕様をオープンソースとして公開している」という所だと思います。ARMアーキテクチャはArm社内部でのみ使用の策定議論が行われ、外部の開発者はARMのいうことに従うほかありません。しかし、RISC-Vの仕様書自体がGitHub上で公開されており、そして私たちは誰でもPull Requestを投げることができます(!)このように、誰でもRISC-Vの仕様の策定に参加できるというのが、RISC-Vの大きな特徴だと言えます。

一つの例として、RISC-VのVector Extension仕様(https://github.com/riscv/riscv-v-spec)には毎週のようにMeeting Minutesがリポジトリ上に追加されています(https://github.com/riscv/riscv-v-spec/tree/master/minutes)。このように、議論の流れもすべて公開されているというのが、RISC-Vの大きな特徴だと言えるでしょう。

私の考える「半導体IPに関する不適切な用語」

まとめとして、私の考える「不適切なRISC-V関連の用語」をまとめておきます。