UCB(University of California, Berkeley)の論文を教えてもらい、読んでみることにした(実際には大量にGoogle翻訳した)。

この論文は"Generating the Next Wave of Custom Silicon"という論文である。 著者から分かる通り、RISC-VとChiselの思いっきり関係者である。

- Generating the Next Wave of Custom Silicon

- Borivoje Nikolić, Elad Alon, Krste Asanović, Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, USA

この論文の要旨はこうだ。時代はDSA(Domain Specific Architecture)だ。そのためには、特定の用途に最適化されたチップを少量多品種で製造する必要がある。 その中で、IPの設計にかかる費用やコストを削減する必要がある。また素早く多品種のチップを製造するために、設計段階からそのメソドロジを変える必要があり、 そのために、

- 「オープンソースのCPUアーキテクチャRISC-V」

- 「柔軟な記述が可能なアーキテクチャジェネレータRocket-Chip」

- 「柔軟なパラメタライズが可能なハードウェア構築言語Chisel」

- 「プロセスをまたいでアナログ回路を生成することができるポータブルアナログ回路ジェネレータBAG2」

を開発した。

それぞれのコンポーネントについて説明する。

オープンな命令セットアーキテクチャで、CPUコアライセンス料やIPライセンス料を削減することができる

- 柔軟なパラメタライズが可能なハードウェア構築言語Chisel

これまでに彼らは様々なハードウェア記述言語(Spiral, Genesis, Chisel)を開発してきたが、ChiselはScalaをベースにしDSL(Domain Specific Language)で、その特徴はハードウェア記述を抽象化できるということである。 また、ライブラリとしてハードウェアコンポーネントを提供できるということだ。ライブラリパッケージとしてDSPのライブラリを開発しており、それらを簡単に結合したり、ハードウェアを再利用することができる。

- 柔軟な記述が可能なアーキテクチャジェネレータRocket-Chip

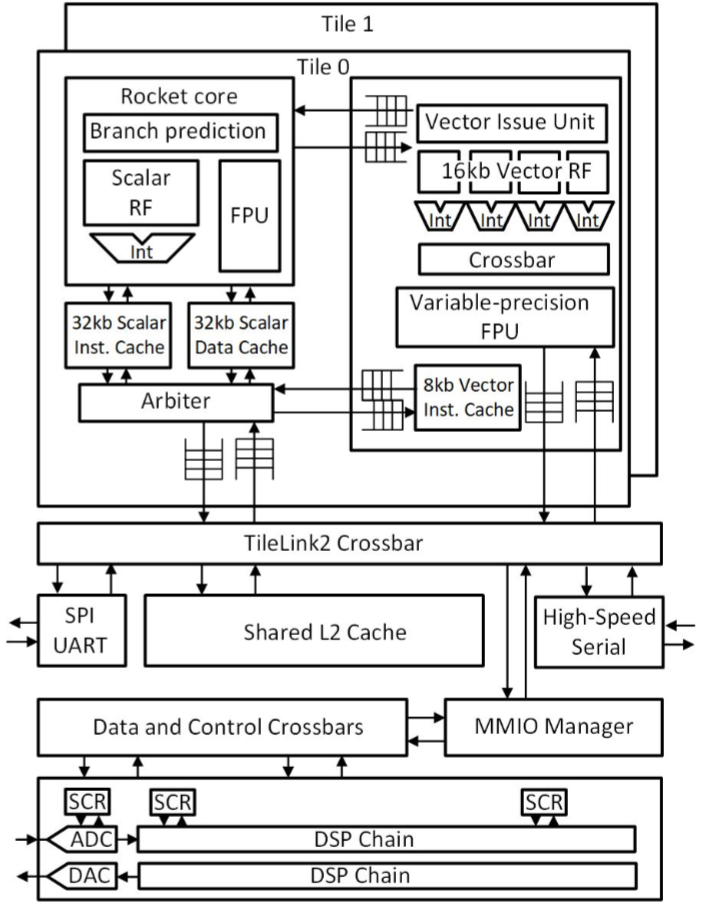

Chiselを活用して、アーキテクチャジェネレータRocket-Chipを開発した。Rocket-ChipはSoCとして活用することができ、共通のバスインタフェースとしてTileLink2を使用している。TileLink2で接続されたコンポーネントは、基本的にどのようなデザインでも再利用できる。

このRocket-Chip Generatorを使用して、例えばRoCCインタフェース(Rocket Custom Coprocessor)を使用した拡張を行うことができる。 以下の図はDSPサブシステムとシリアルリンクをRocket-Chipに追加したマルチコアプロセッサシステムである。このようなシステムを簡単に構築できる。

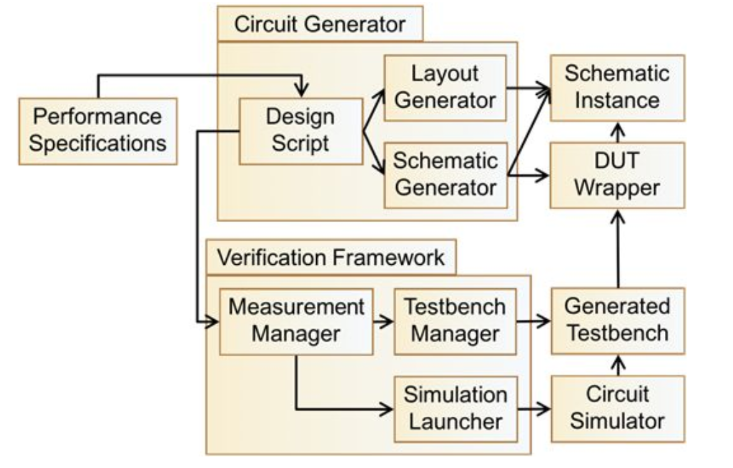

- プロセスをまたいでアナログ回路を生成することができるポータブルアナログ回路ジェネレータBAG2

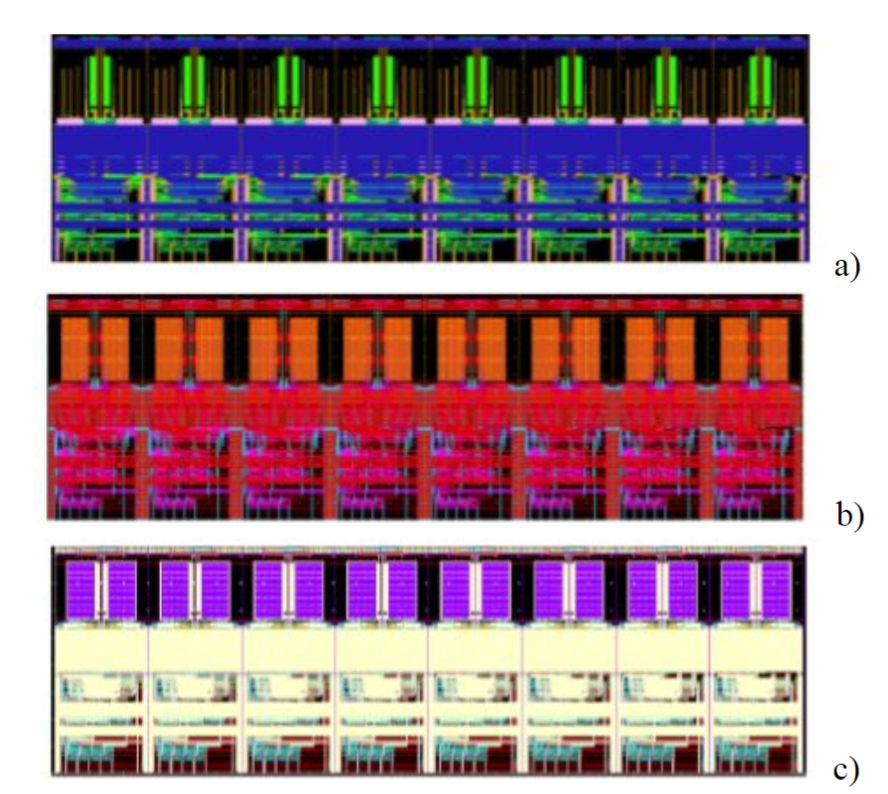

BAG2はBerkeley Analog Generatorで、Pythonベースのプロセスをまたぐアナログ回路のジェネレータである。 このBAG2にはAPI、設計スクリプト、レイアウト生成エンジンなどを含んでおり、イコライザやSerDesなどを設計している。 これまでにSTマイクロの28FDSOI、GFの22FDX, TSMC 16FFCなどに対してBAG2によりアナログ回路を移植してきた。

これらの要素を組み合わせることで、プロセスを変えながら短いイタレーションでチップを数多くテープアウトしてきた。これが次の時代のチップ設計の手法だ、というのが本論文の趣旨である。

まあ言いたいことは分かる。ただオープンソースとパラメタライズできるハードウェア構築言語で解決できる問題って、半導体設計・製造の深い闇の中でもかなり上流工程だけに過ぎない。 実際に本気でチップを作るときにもっとも時間がかかるのはやはりバックエンド、レイアウトだということを痛感することも多い。 チップをどのようにレイアウトするのか、クロックはどのように張るか、どのようにモジュールを配置するかというところが重要になる。 これらの問題は、フロントエンドではおいそれと解決できない闇がある。

そこにも、メスが入ってほしいというのは事実だ。現状の業界構成を見ても、大きなEDAベンダは2社しかいない。 この2社が互いにけん制しあって、新規技術に力を注がない、ライセンス料は互いにけん制して高いまま、これでは進化するゆとりがない。

本音を言えばこの2社ははやいところ潰れてもらって、競争力を上げるためにより多くのベンダに参入してもらい、技術競争をした方が業界構造としてはまともに思える。

ChiselやRocket-Chipは、たしかにハードウェア設計という面で一つの波になるのかもしれない。 しかしそれをうまく活用できるかというのはまた謎だ。UCBの優秀な学生はChiselを使いこなすかもしれないが、Chiselの本来の力をすべての技術者が発揮できるかというのは別問題だ。Rocketの究極的なカスタマイズのメソドロジをすべての技術者が理解できるわけではない。 Chiselを実際に使ってみると、どうしてもいろんな問題にぶち当たるし、まだ開発環境がしっかりしているわけではない。問題は山積している。

半導体業界に表れたこの小さな波が消えてしまわないように、半導体業界全体を巻き込んでどうにかして大きな波にしてほしい。

私は決してRISC-VとChiselを手放しで褒めちぎるつもりは無い。 今後もこのような技術の調査を進めるし、いろんな技術を公平に見ていきたいものだ。