RISC-V Workshop Zurichで発表された、RISC-Vのオープンソースのプロセッサコアと環境を提供するためのグループ、OpenHWの概要が発表され、その資料を読んだ。

- OpenHW Group Proven Processor IP Corporate & CORE-V Overview

OpenHWグループとは

OpenHWグループは非営利のグルーバル団体であり、ハードウェアとソフトウェアのデザイナがコラボレーションしてオープンソースコア、関連するIP、ソフトウェアなどのツールを開発するための団体である。より品質の高いオープンソースハードウェアを提供することが目的となる。

CORE-VシリーズはRISC-Vをベースとしたオープンソースのコアおよびサブシステム、そしてソフトウェアツールなどの集合体である。CORE-Vファミリは品質の高いオープンソースコアを提供することを目的とする。

- オープンソースプロセッサコアのロードマップを公式に作成する。

- プロセッサコアおよびハードウェア/ソフトウェアエコシステムの維持、進化、およびオープンソースライセンスを担当します。

- ユーザーコミュニティの技術やニーズの変化に対応する

- 商標または認証マークのライセンスを管理することで、プロジェクトまたは製品がそのマークを使用できるかどうかを決定します。

メンバーシップ・コントリビュータ

- プラチナメンバ - 多くの投資+最大3人までのアクティブなコントリビュータ

- ゴールドメンバ - Mediumな投資 + 2人までのアクティブなコントリビュータ

- シルバーメンバ - Smallな投資

- テクニカル・マーケティングワーキンググループとサブタスクグループに参加することができる。

- プラチナ・ゴールド・シルバーメンバは所属しているワーキンググループの投票権を、1人1票持っている。

- アソシエイト メンバ(投票権を持たない)

- テクニカル・マーケティング ワーキンググループとサブタスクグループへの参加する権利を持つ。

複数の多国籍なパートナーから構成される

OpenHWグループの初期スポンサー

SoC開発に必要なコスト

- ソフトウェア、RTL設計、検証、物理設計がSoC設計に必要なコストの90%を占める。

- 高度に差別化されたIPブロックと機能であれば、この投資は問題ないが、汎用CPUはオープンソースモデルを使用することでこれらのコストを削減できないか?

どのような問題を解決しようとしているのか?

- IPの品質

- ハーネスコミュニティ最高クラスの設計と検証の貢献

- エコシステム

- 許容された用途

- ビジネス上、および法律上のリスクを最小化するために寛容なオープンソースライセンスとする。

RISC-VのCORE-Vファミリ

ETH ZurichのPULP Platformから、RISC-Vコアの最初の提供を受ける

- Ri5cy : 32-bit, 4ステージパイプライン, RV32IMC (https://github.com/pulp-platform/riscv)

- Ariane : 64-bit, 6ステージパイプライン, RV64IMCD (https://github.com/pulp-platform/ariane)

ワーキンググループ

- テクニカルワーキンググループ

- コアタスクグループ

- コアIPのロードマップをおよび各種アプリケーション向けのISAおよびマイクロアーキテクチャを定義する。

- ロードマップに基づき、新しいコアIPなどを開発する。

- コアIPのロードマップをおよび各種アプリケーション向けのISAおよびマイクロアーキテクチャを定義する。

- 検証タスクグループ

- プラットフォームタスクグループ

- コアタスクグループ

- マーケティングワーキンググループ

- コンテントタスクグループ

- イベントタスクグループ

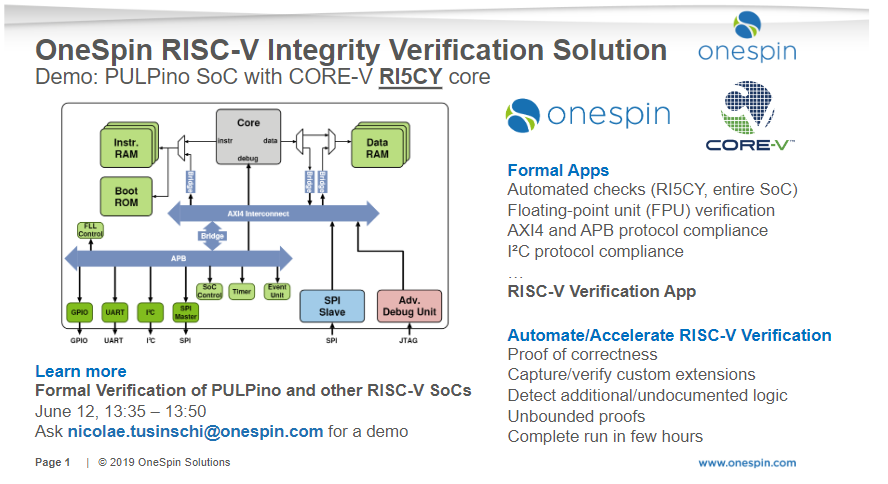

デモンストレーション

- CORE-V NXP VEGA

- RI5CY、Cortex-M4F、Zero-RISCY、Cortex-M0+のチップ

- GreenWaveのCORE-Vデモ : GAP-8

- OpeSpin CORE-V