MLIRについてもう少し具体的な例を勉強するために、資料を読み込んでいくことにした。前回の続き。

以下の資料を参考にした。Chris Lattnerの所属がSiFiveに変わっているので、比較的最近の資料だ。

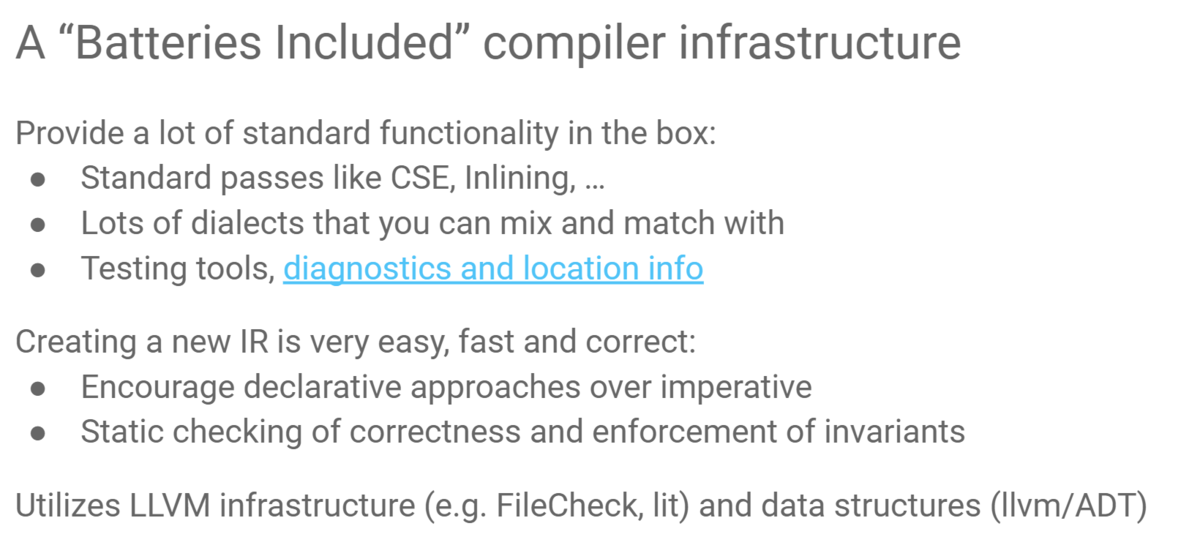

MLIR Infrastructureについて

この"Batteries Included"というのは、自分自身がオペレーションを定義することができる、ということだと思う。

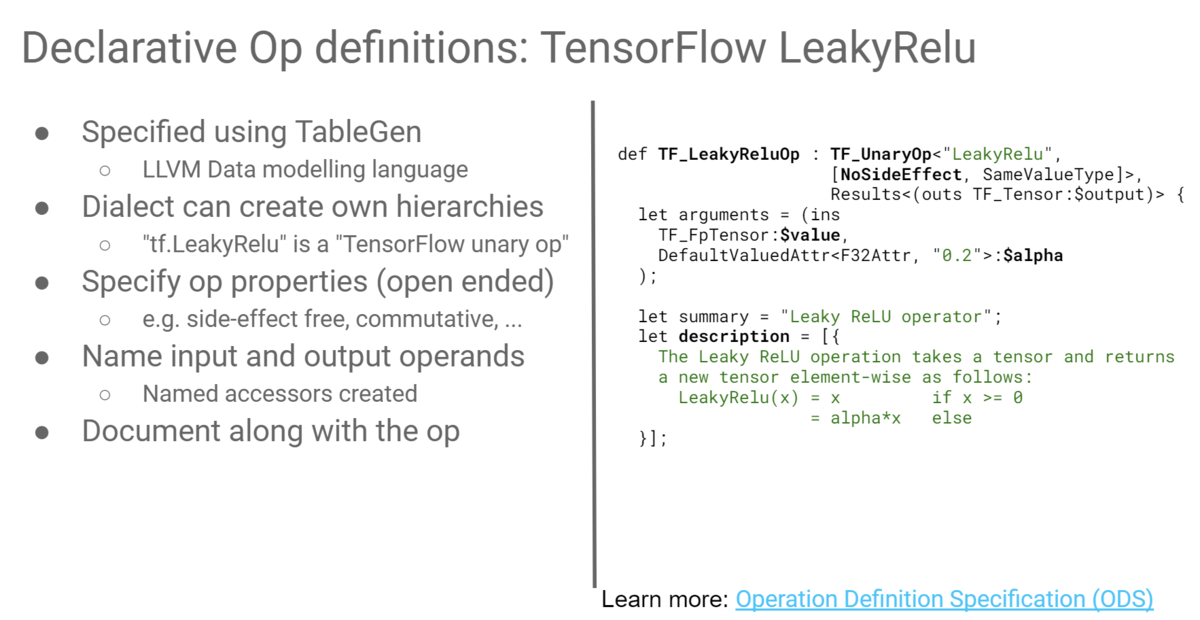

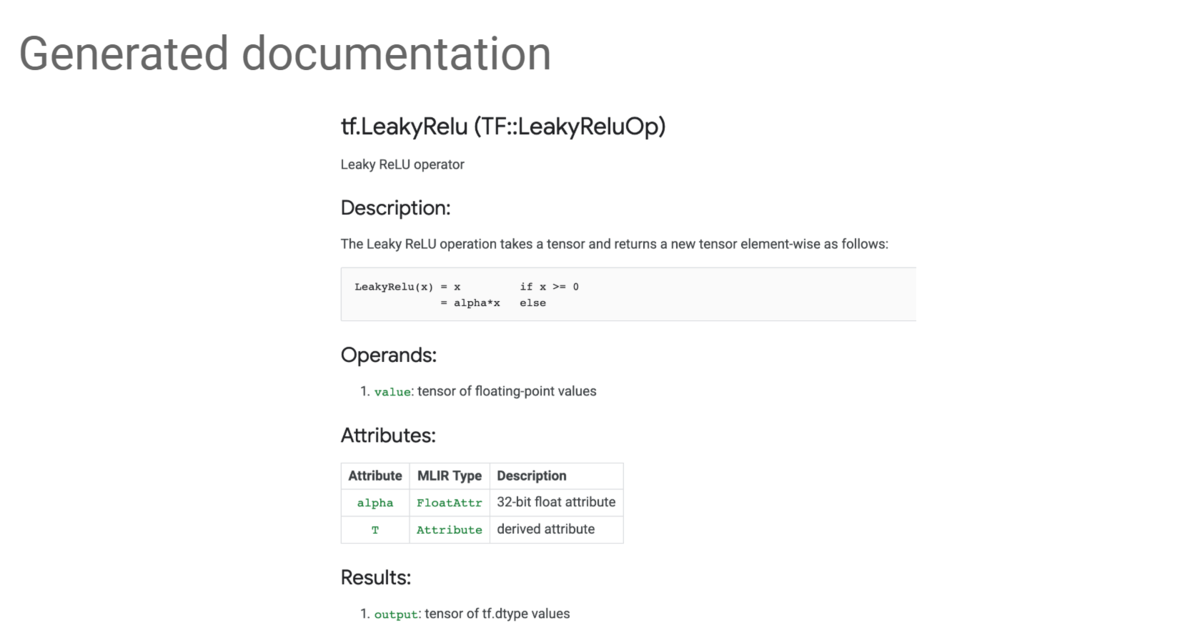

Op definitionの例ということで、TensorFlowのLeakyReluの例が出てくる。

TableGenによって定義されるDSLなのだが、まずはTF_LeakyReluOpは"TensorFlowの単項演算子である"という定義がなされている。プロパティの設定(パラメータの設定のようなもの:NoSideEffects)が行われている。Opの定義はSameValueTypeで指定されているのだろうか。入力と出力オペランドの形はlet argumentsで指定されているようだ。最後にドキュメントが指定されている。

これにより、自動的にドキュメントが生成されるという仕組みになっているようだ。

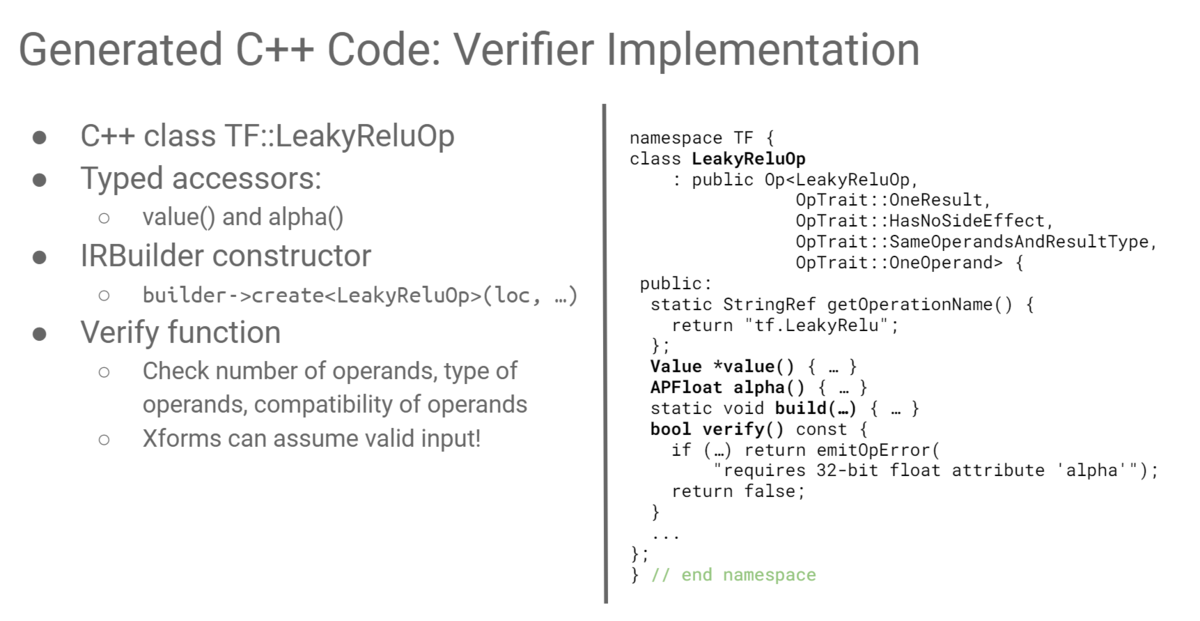

このDSLからC++のコードが出力されるわけだが、これにはCheker(Verifier)まで一緒に実装されているらしい。アサーションが自動的に挿入されているという仕組みかな。

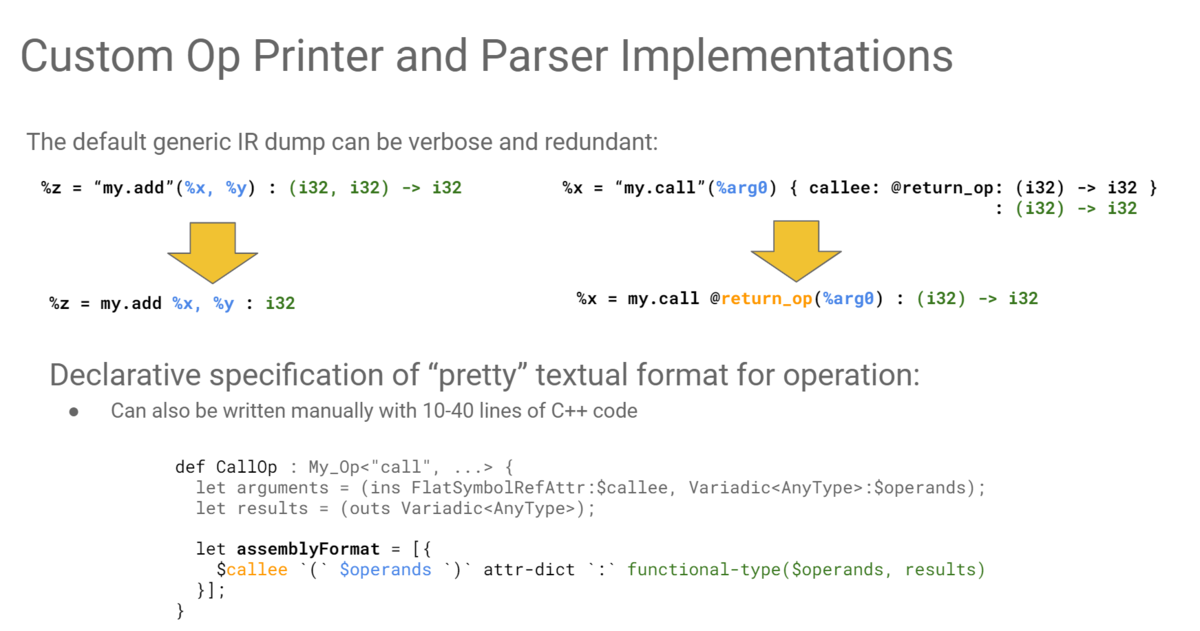

Opのダンプ用のコードやParserをassemblyFormatで指定することができるということか?

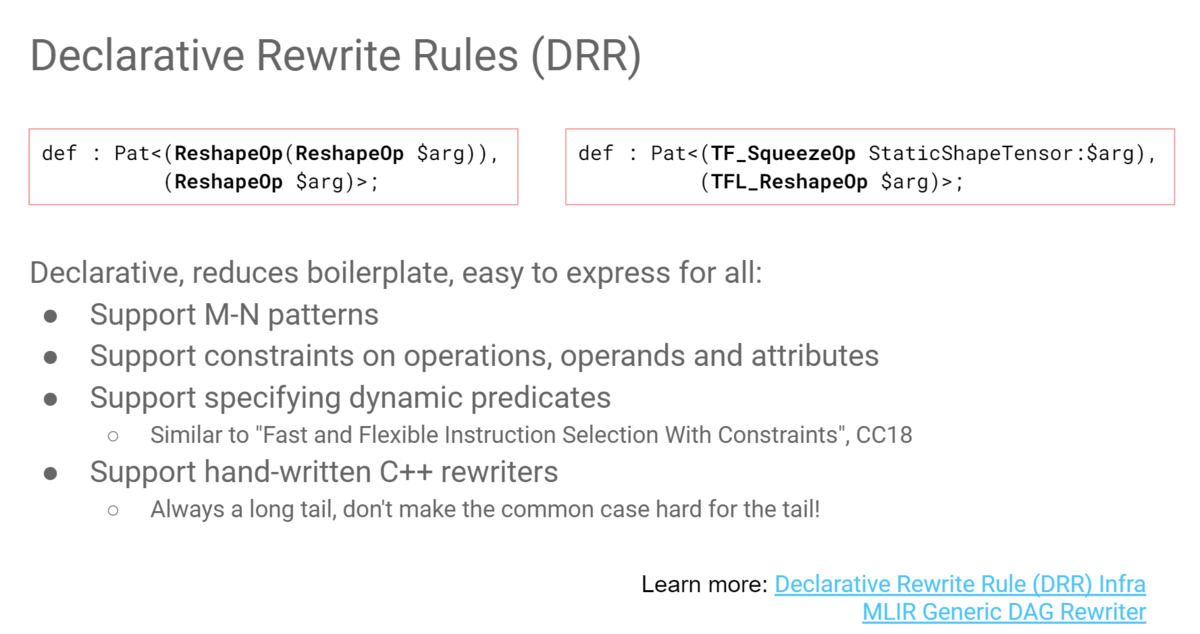

Declarative Rewrite Rules(DDR)。これはLLVMのRewrite Ruleと大して変わらないのだろうか?

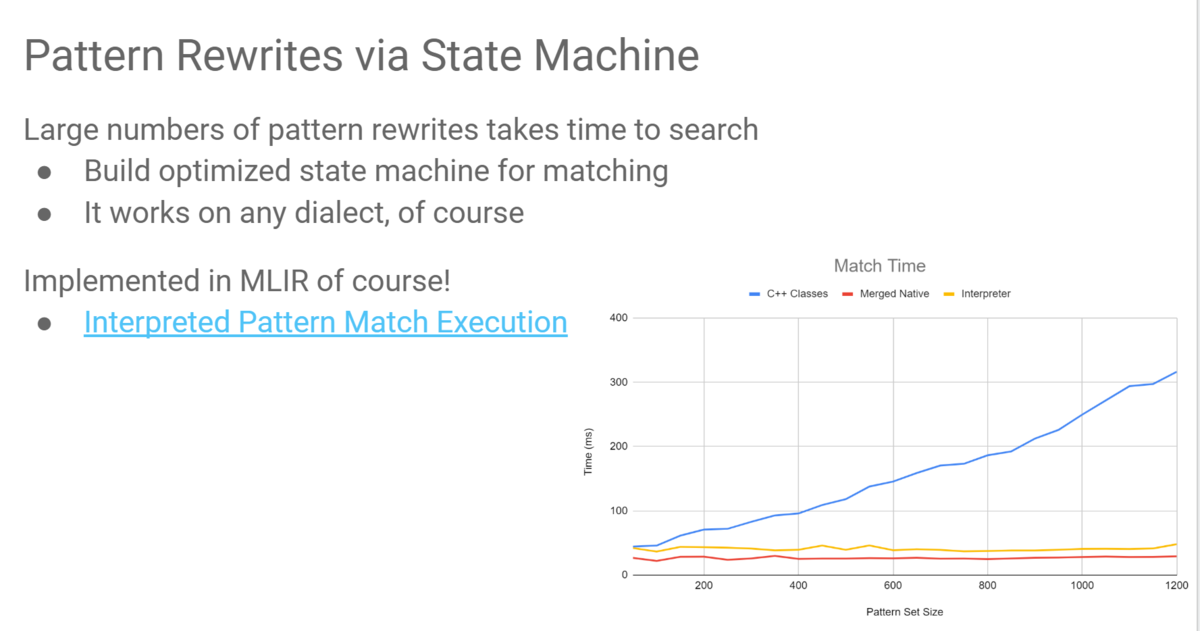

で、このRewriteのルールを大量に記述すると動作が遅くなるらしい。これをステートマシンに変換して速度を改善すると書いてあるが、詳しいことは正直良く分からない。

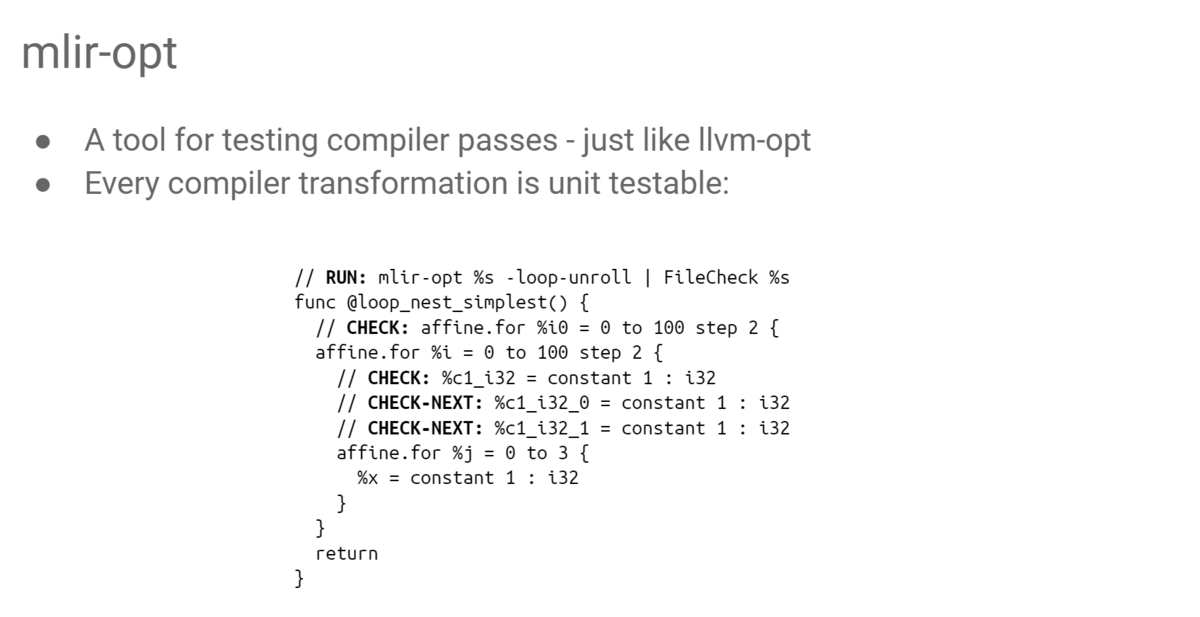

mlir-optはコンパイラのPassをテストするためのフレームワーク。llvm-optと同様。

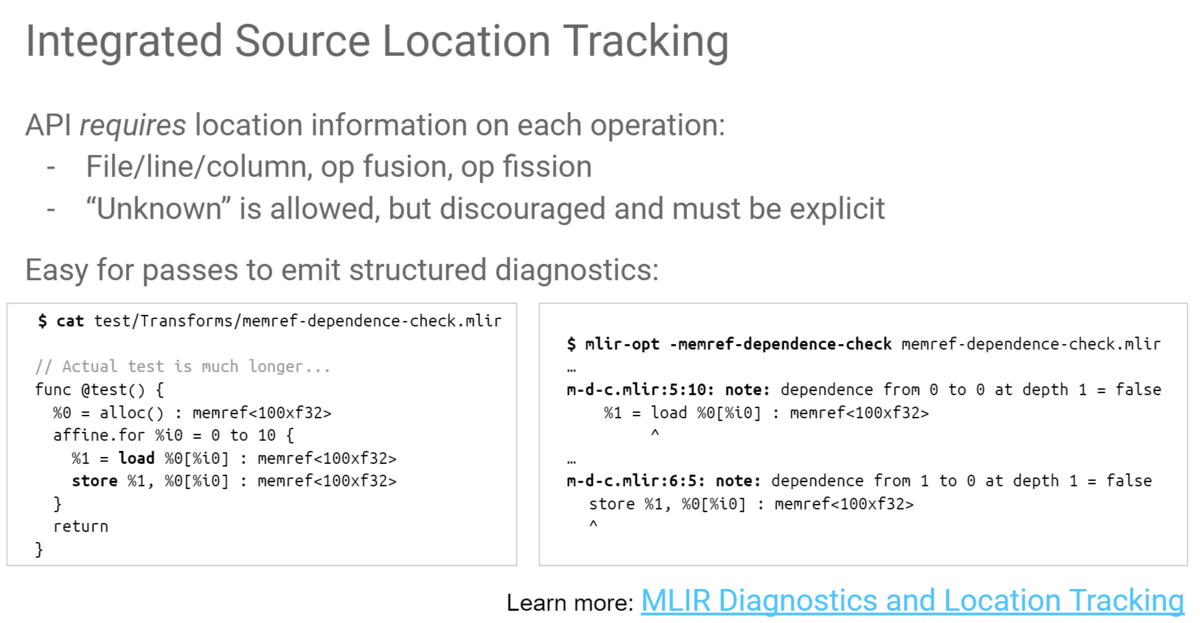

デバッグ機能。ソースロケーショントラッキング。これはLLVM IRにも付いている奴かな?

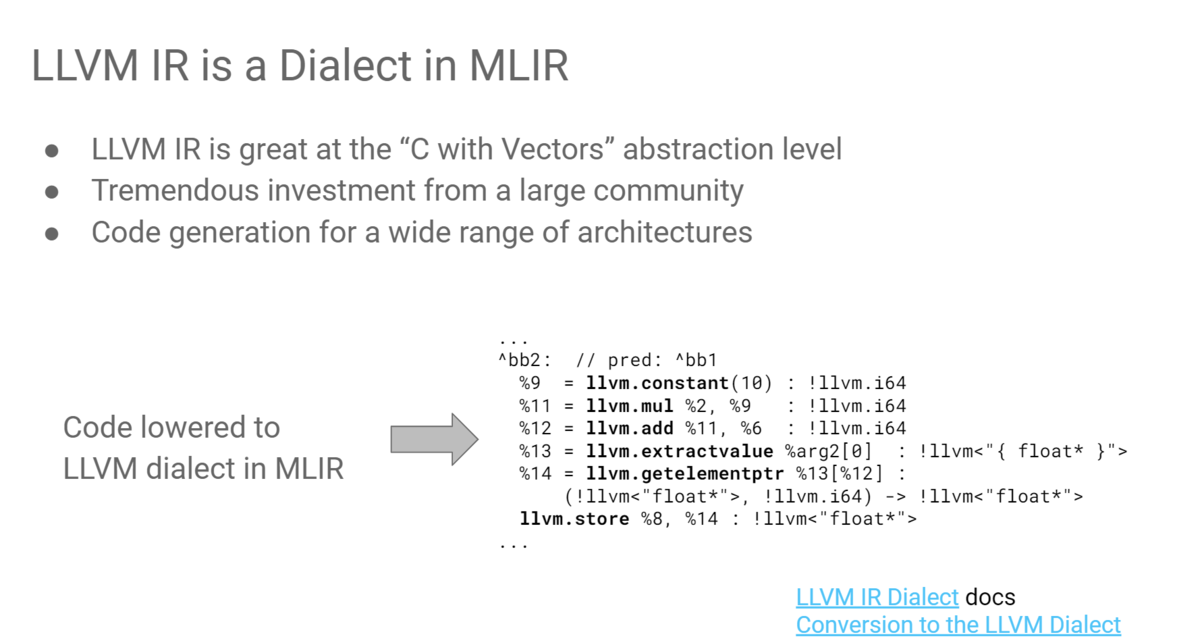

そして、MLIRはLLVM IRを方言として受け付けることができるらしい。LLVM IRは「ベクトル付きのC」と言われているくらいあって、あまりレイヤが高くないのでこれを受け取ることができる。