CARRVで発表された、UCBのRISC-V FPGAシミュレーション環境 MIDASのリポジトリがあったので、実験してみた。

試してみたのは以下のディレクトリ。

まずは一応全部ダウンロードした。riscv-fesvrを最新に更新しないと動作しないようなので、riscv-fesvrを更新する。

git clone https://github.com/ucb-bar/midas-top-release.git

cd midas-top

./setup.sh

しかしこのリポジトリまだきちんと管理されていないのか、サブリポジトリのダウンロードができないので少し変更した。

diff --git a/.gitmodules b/.gitmodules index 1e1dad0..9b1170d 100644 --- a/.gitmodules +++ b/.gitmodules @@ -1,24 +1,24 @@ [submodule "rocket-chip"] path = rocket-chip - url = git@github.com:ucb-bar/rocket-chip.git + url = https://github.com/ucb-bar/rocket-chip.git [submodule "midas"] path = midas - url = git@github.com:ucb-bar/midas-release.git + url = https://github.com/ucb-bar/midas-release.git [submodule "firrtl"] path = firrtl - url = git@github.com:ucb-bar/firrtl.git + url = https://github.com/ucb-bar/firrtl.git [submodule "chisel"] path = chisel - url = git@github.com:ucb-bar/chisel3.git + url = https://github.com/ucb-bar/chisel3.git [submodule "riscv-boom"] path = boom - url = git@github.com:ucb-bar/riscv-boom.git + url = https://github.com/ucb-bar/riscv-boom.git [submodule "midas-zynq"] path = platforms/zynq - url = git@github.com:ucb-bar/midas-zynq.git + url = https://github.com/ucb-bar/midas-zynq.git [submodule "fesvr"] path = riscv-fesvr - url = git@github.com:riscv/riscv-fesvr.git + url = https://github.com/riscv/riscv-fesvr.git

あとはriscv-fesvrのリポジトリ更新を行っておく。

cd riscv-fesvr ./configure --prefix=/home/msyksphinz/riscv64/ make make install

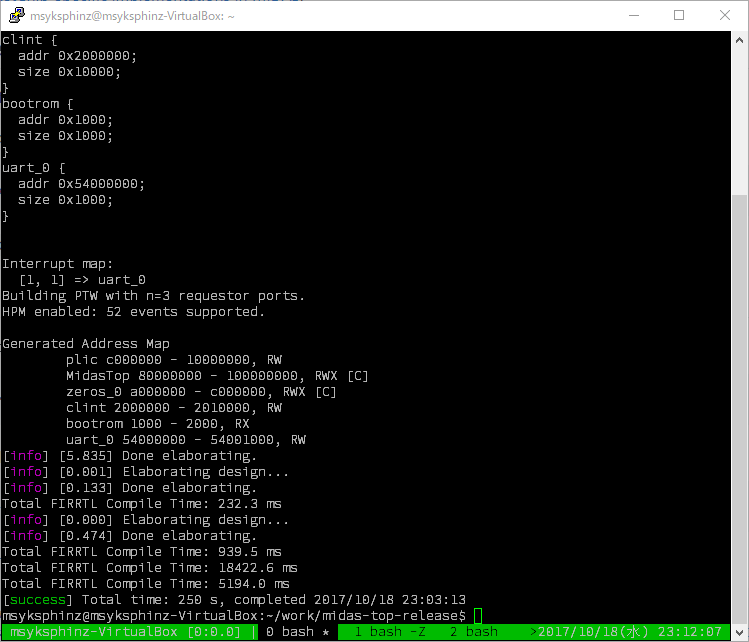

make verilogの実行結果

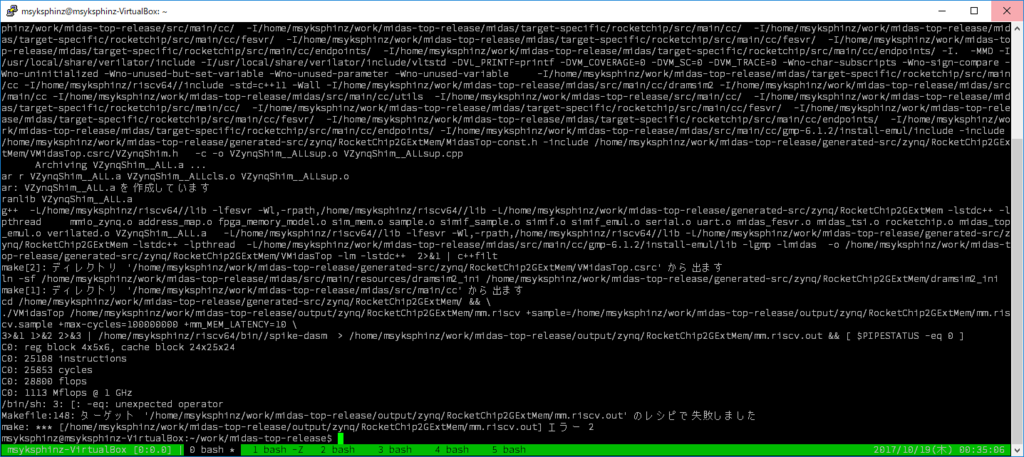

make run-bmark-testsの実行結果

なぜか1本目でシミュレーションが止まるね。原因が良く分からないけど、とりあえずMakefileを改造する。

$(output_dir)/%.out: $(output_dir)/% $(EMUL)

cd $(dir $($(EMUL))) && \

./$(notdir $($(EMUL))) $< +sample=$<.sample +max-cycles=$(timeout_cycles) $(SW_SIM_ARGS) \

- $(disasm) $@ && [ $$PIPESTATUS -eq 0 ]

+ $(disasm) $@

make bitstream BOARD=zedboardの実行結果。Vivadoで確認してみる。