RISC-Vの実装としていろいろ調査している中で、Parallelaのホストボードとして利用されているZynq(またはZedBoard)上にRISC-Vを移植してアプリケーションを動作させるというプロジェクトを発見した。

Google Summer of Codeのプロジェクトの一つだったようだ。

これは、Parallelaのホスト制御プロセッサとして利用されているZynqにRISC-Vを移植するというもので、プロジェクトの概要を上記プロジェクトページから引用すると、

This project will focus on the integration of the RISC-V rocket core, inside the Zynq FPGA device of Parallela.

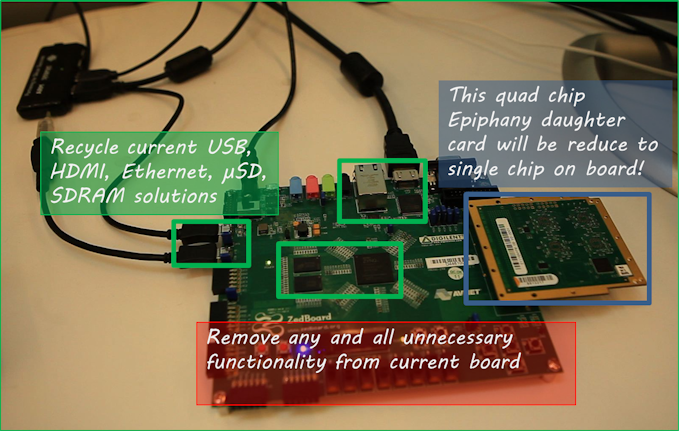

このプロジェクトをきちんと調査するまでは、ParallelaとZynq、RISC-Vがどのような関係なのか全くわからなかったが、以下の写真があるようにParallelaとZynq FPGAは密接に関係がある。

(https://www.kickstarter.com/projects/adapteva/parallella-a-supercomputer-for-everyone より引用)

プロジェクトの成果として、Zynqデザインの中にRISC-Vを統合することは完了したようだ。 ただし、そこから具体的に何か新しいアプリケーションを動作させたかというとちょっと分からない。

プロジェクトのやる事自体は分かるのだが、目的がいまいちよく分からない。。。 ARMがあるならそれを使えばよいし、わざわざ低速なRISC-V IPを使う理由は良く分からないが。。。

ちなみに、成果リポジトリは以下にアップロードされている。

GitHub - eliaskousk/parallella-riscv: RISC-V port to Parallella Board