RISC-VのオープンソースプロセッサBOOMv3(SonicBOOM)が公開されているが、シミュレーションを行うためにはChipyardの環境を用意するのが原則になっているようだ。

SonicBOOMv3のリポジトリ事態にCoremarkは入っていないようなので自分でバイナリを構築する必要があるらしい。が、CoremarkのRISC-V向けビルド環境があるらしい。

pk向けのバイナリとBaremetalのバイナリの両方が作れるらしい。これをダウンロードしてビルドしておけばよいのか。

git clone https://github.com/riscv-boom/riscv-coremark.git cd riscv-coremark git submodule update --init --recursive ./build-coremark.sh

一応ログを出したいので、BOOMをログ付きでビルドしておく。

src/main/scala/common/parameters.scala

diff --git a/src/main/scala/common/parameters.scala b/src/main/scala/common/parameters.scala index 1a0c25fd..8d7c910c 100644 --- a/src/main/scala/common/parameters.scala +++ b/src/main/scala/common/parameters.scala @@ -92,7 +92,7 @@ case class BoomCoreParams( clockGate: Boolean = false, /* debug stuff */ - enableCommitLogPrintf: Boolean = false, + enableCommitLogPrintf: Boolean = true, enableBranchPrintf: Boolean = false, enableMemtracePrintf: Boolean = false

で、そのままVerilatorのバイナリに流して実行する。CMK値は 3.83CMK/MHz となった。

cd sims/verilator/ make CONFIG=MediumBoomConfig ./simulator-chipyard-MediumBoomConfig +verbose ../../riscv-coremark/coremark.bare.riscv >& coremark.medium.riscv.log

全部ログがcoremark.medium.riscv.logに出てきてしまうので、grepして抽出する。

grep -v ^3 coremark.bare.riscv.log

using random seed 1592581205

This emulator compiled with JTAG Remote Bitbang client. To enable, use +jtag_rbb_enable=1.

Listening on port 55449

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 2608224

Total time (secs): %f

Iterations/Sec : %f

ERROR! Must execute for at least 10 secs for a valid result!

Iterations : 10

Compiler version : GCC9.2.0

Compiler flags : -O2 -mcmodel=medany -static -std=gnu99 -fno-c3 0x00000000800025b4 (0xdf7d)

ommon -nostdlib -nostartfiles -lm -lgcc -T ../riscv64-baremetal/3 0x00000000800025b4 (0xdf7d)

link.ld

Memory location : Please put data memory location here

(e.g. code in flash, data on heap etc)

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0xfcaf

Errors detected

*** PASSED *** Completed after 2659834 cycles

[UART] UART0 is here (stdin/stdout).

ついでにMegaBoomConfigも試してみる(最大構成)。CMK値は 5.33 CMK/MHz となった。

./simulator-chipyard-MegaBoomConfig +verbose ../../riscv-coremark/coremark.bare.riscv >& coremark.mega.riscv.log

using random seed 1592619488

This emulator compiled with JTAG Remote Bitbang client. To enable, use +jtag_rbb_enable=1.

Listening on port 59775

2K performance run parameters for coremark.

CoreMark Size : 666

Total ticks : 1873606

Total time (secs): %f

Iterations/Sec : %f

ERROR! Must execute for at least 10 secs for a valid result!

Iterations : 10

Compiler version : GCC9.2.0

Compiler flags : -O2 -mcmodel=medany -static -std=gnu99 -fno-c3 0x00000000800025b2 (0x6298) x14 0x0000000000000000

ommon -nostdlib -nostartfiles -lm -lgcc -T ../riscv64-baremetal/3 0x00000000800025b4 (0xdf7d)

link.ld

Memory location : Please put data memory location here

(e.g. code in flash, data on heap etc)

seedcrc : 0xe9f5

[0]crclist : 0xe714

[0]crcmatrix : 0x1fd7

[0]crcstate : 0x8e3a

[0]crcfinal : 0xfcaf

Errors detected

*** PASSED *** Completed after 1917263 cycles

[UART] UART0 is here (stdin/stdout).

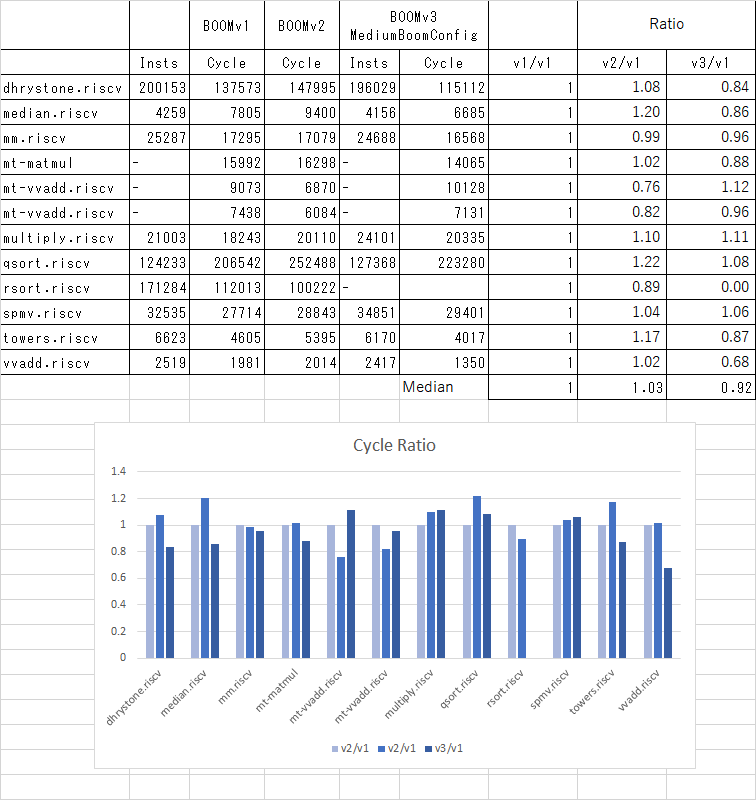

ベンチマークをすべて流してみても、全体的にMegaBoomConfigはMediumBoomConfigよりも高速だ。1.5倍くらいのサイクル性能向上かな。