RISC-VのアウトオブオーダプロセッサであるBOOMのVersion 2.2がリリースされた。

リリース通知から、アップデート内容を確認してみると、

- 全てのコンフィグレーションでRISC-V Compressed("RVC")命令をサポート

- これでBOOM専用にRV64Gのツールチェインをビルドする必要が無くなる。

- BOOMでFedoraのディスクイメージがブートできるようになった。 http://fedora-riscv.tranquillity.se/koji/

- PMPレジスタのサポート

- ノンブロッキングL1キャッシュはRocket-Chipからフォークされた。

- これはPMPサポートのために必要。しかしさらに強力なDCacheを搭載する予定。

- マイナーなCSR命令の修正

- ReadTheDocs documentation を作成 https://docs.boom-core.org/en/latest/

- ウェブサイトを作り直し boom-core.org

- BOOMのリポジトリはriscv-boomに移動しなおした。

- これまではEsperantoTechのリポジトリとして管理されていたのだが、riscv-boomに戻ったのか。

- BOOMによるSpectre攻撃のデモンストレーション https://github.com/riscv-boom/boom-attacks

- CircleCIによるCI環境の構築

- Chisel3の構文に書き換えを実施。

これはなかなかに面白そうだ。早速、使ってみよう。

ちなみに、今回はリビジョン 1e5bc7c を使って動作確認を行った。

ドキュメントは以下にすべて用意されている。といってもこれは内部パイプラインのドキュメントだ。これは便利。

ビルドの方法はこれまでの通り。資料を見ながら進める。

git clone https://github.com/riscv-boom/boom-template.git cd boom-template ./scripts/init-submodules.sh export RISCV=${HOME}/riscv_boomv22 export PATH=$RISCV/bin:$PATH ./scripts/build-tools.sh

これで、環境が整ったのでVerilatorでビルドし、シミュレーションを実行してみる。

cd verisim

make

早速Dhrystoneを実行したのだが、途中で失敗してしまった。

make output/dhrystone.riscv.out

- output/dhrystone.riscv.out

using random seed 1548641781

This emulator compiled with JTAG Remote Bitbang client. To enable, use +jtag_rbb_enable=1.

Listening on port 61599

first_pc: 0x0080001140 last_npc: 0x0080001142 Assertion failed: [fetchmonitor] A non-cfi instruction is followed by the wrong instruction.

at fetchmonitor.scala:146 assert (first_pc === last_npc,

そこで、COMMITログをONにして様子を見てみることにした。

diff --git a/src/main/scala/common/consts.scala b/src/main/scala/common/consts.scala index 3abc41d..78c7ca8 100755 --- a/src/main/scala/common/consts.scala +++ b/src/main/scala/common/consts.scala @@ -23,7 +23,7 @@ import freechips.rocketchip.util.Str trait BOOMDebugConstants { val DEBUG_PRINTF = false // use the Chisel printf functionality - val COMMIT_LOG_PRINTF = false // dump commit state, for comparision against ISA sim + val COMMIT_LOG_PRINTF = true // dump commit state, for comparision against ISA sim val O3PIPEVIEW_PRINTF = false // dump trace for O3PipeView from gem5 val O3_CYCLE_TIME = (1000)// "cycle" time expected by o3pipeview.py

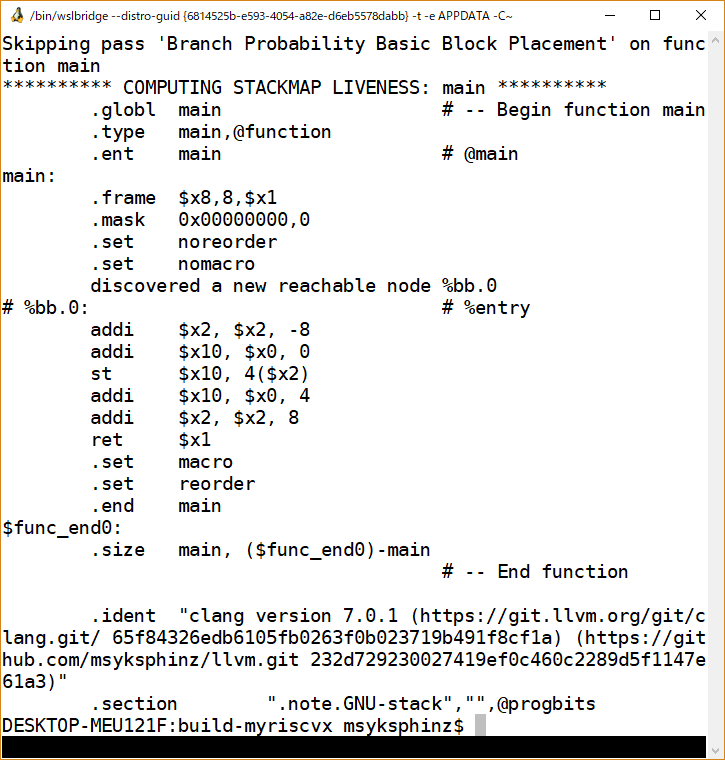

Dhrystoneの実行結果のログを確認すると、以下の命令を実行して停止している。

3 0x0000000080001b32 (0x84818d13) x26 0x00000000800028f0

3 0x0000000080001b36 (0x00001997) x19 0x0000000080002b36

3 0x0000000080001b3a (0xda298993) x19 0x00000000800028d8

3 0x0000000080001b3e (0x490a1497) x 9 0x00000000c90a2b3e

first_pc: 0x0080001b40 last_npc: 0x0080001b42 Assertion failed: [fetchmonitor] A non-cfi instruction is followed by the wrong instruction.

at fetchmonitor.scala:146 assert (first_pc === last_npc,

うーん、0x1b3eの次は0x1b42で、その周辺も命令も問題なさそうだが、、、

riscv64-unknown-elf-objdump -D dhrystone.riscv | less

...

80001b32: 84818d13 addi s10,gp,-1976 # 800028f0 <Ptr_Glob>

80001b36: 00001997 auipc s3,0x1

80001b3a: da298993 addi s3,s3,-606 # 800028d8 <Ch_2_Glob>

80001b3e: 00001497 auipc s1,0x1

80001b42: baa48493 addi s1,s1,-1110 # 800026e8 <main+0xcfc>

80001b46: f3043903 ld s2,-208(s0)

80001b4a: 00000517 auipc a0,0x0

80001b4e: 67e50513 addi a0,a0,1662 # 800021c8 <main+0x7dc>

80001b52: 85ca mv a1,s2

80001b54: e24ff0ef jal ra,80001178 <debug_printf>

80001b58: 4505 li a0,1

GitHubのページにはrv64ui-p-addの結果のみ書いてあるのだが、まだ調整が必要なのかな。