全く資料が無いのだが、RISC-V実装であるRocket-Chipでは、リグレッションスイートが格納されているregression/というディレクトリが存在する。

make emulator-regression-tests SUITE=UnittestSuite

まずはAMBAのテストを実行してみるためにいくつかテストを削減する。

AMBAUnitTestConfigのみを実行する。

diff --git a/regression/Makefile b/regression/Makefile index 7953daa6..43b1e85c 100644 --- a/regression/Makefile +++ b/regression/Makefile @@ -58,7 +58,8 @@ endif ifeq ($(SUITE),UnittestSuite) PROJECT=freechips.rocketchip.unittest -CONFIGS=AMBAUnitTestConfig TLSimpleUnitTestConfig TLWidthUnitTestConfig +CONFIGS=AMBAUnitTestConfig endif

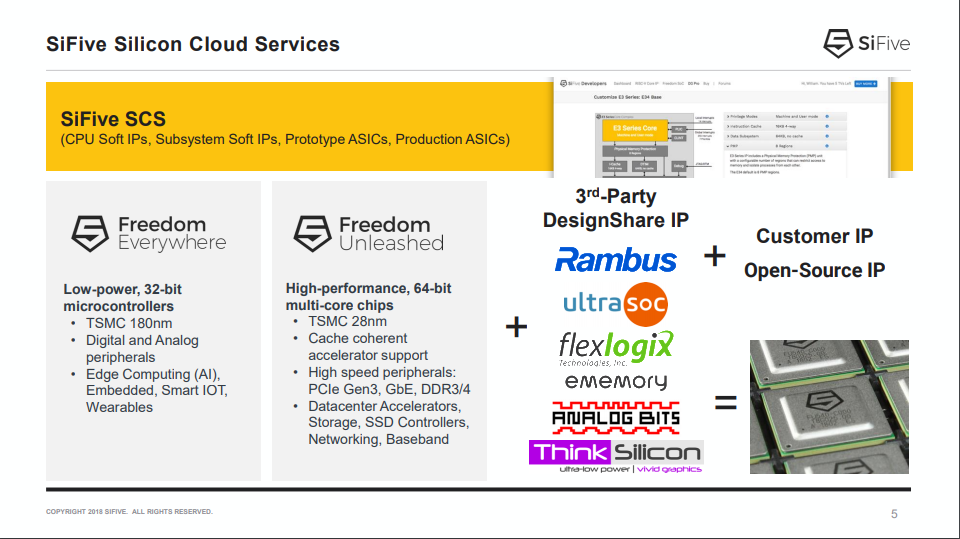

この辺について、Chiselでどのようにテストを構成すればいいのか良く分かっていないのだが、TestHarnessにAMBAの実装を当てはめて、テストのコンフィグレーションを挿入するらしい。

rocket-chip/src/main/scala/unittest/Configs.scala

class AMBAUnitTestConfig extends Config(new WithAMBAUnitTests ++ new WithTestDuration(10) ++ new BaseSubsystemConfig)

WithAMBAUnitTestsの実装は以下のようになっている。

class WithAMBAUnitTests extends Config((site, here, up) => { case UnitTests => (q: Parameters) => { implicit val p = q val txns = 100 * site(TestDurationMultiplier) val timeout = 50000 * site(TestDurationMultiplier) Seq( Module(new AHBBridgeTest(true, txns=8*txns, timeout=timeout)), Module(new AHBNativeTest(true, txns=6*txns, timeout=timeout)), Module(new AHBNativeTest(false,txns=6*txns, timeout=timeout)), Module(new APBBridgeTest(true, txns=6*txns, timeout=timeout)), Module(new APBBridgeTest(false,txns=6*txns, timeout=timeout)), Module(new AXI4LiteFuzzRAMTest(txns=6*txns, timeout=timeout)), Module(new AXI4FullFuzzRAMTest(txns=3*txns, timeout=timeout)), Module(new AXI4BridgeTest( txns=3*txns, timeout=timeout)), Module(new AXI4XbarTest( txns=1*txns, timeout=timeout)), Module(new AXI4RAMAsyncCrossingTest(txns=3*txns, timeout=timeout))) } })

例えば AXI4BridgeTestについて実装を見てみた。

rocket-chip/src/main/scala/amba/axi4/Test.scala

class AXI4BridgeTest(txns: Int = 5000, timeout: Int = 500000)(implicit p: Parameters) extends UnitTest(timeout) { val dut = Module(LazyModule(new AXI4FuzzBridge(txns)).module) io.finished := dut.io.finished } ... class AXI4FuzzBridge(txns: Int)(implicit p: Parameters) extends LazyModule { val master = LazyModule(new AXI4FuzzMaster(txns)) val slave = LazyModule(new AXI4FuzzSlave) slave.node := master.node lazy val module = new LazyModuleImp(this) with UnitTestModule { io.finished := master.module.io.finished } }

以下をmakeを実行するとgenerated-srcディレクトリに生成されたVerilogが格納された。

cd regression make emulator-regression-tests SUITE=UnittestSuite cd ../emulator/generated-src $ ls -1 freechips.rocketchip.unittest.AMBAUnitTestConfig freechips.rocketchip.unittest.AMBAUnitTestConfig.anno.json freechips.rocketchip.unittest.AMBAUnitTestConfig.behav_srams.v freechips.rocketchip.unittest.AMBAUnitTestConfig.conf freechips.rocketchip.unittest.AMBAUnitTestConfig.d freechips.rocketchip.unittest.AMBAUnitTestConfig.fir freechips.rocketchip.unittest.AMBAUnitTestConfig.plusArgs freechips.rocketchip.unittest.AMBAUnitTestConfig.v

これからどのようにしてテストスイートを実行すればよいのだろう?

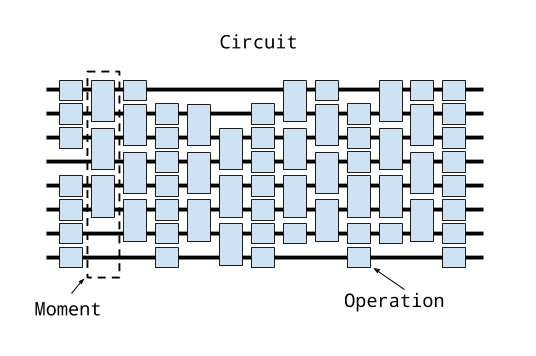

色々解析した結果、全てのテストが同時に動作してテストを実施しているらしい。 つまり、上記の - AHBBridgeTest - AHBNativeTest - AHBNativeTest - APBBridgeTest - APBBridgeTest - AXI4LiteFuzzRAMTest - AXI4FullFuzzRAMTest - AXI4BridgeTest - AXI4XbarTest - AXI4RAMAsyncCrossingTest

それぞれが勝手にMasterとSlaveを作ってテストを実行しているっていうことか。

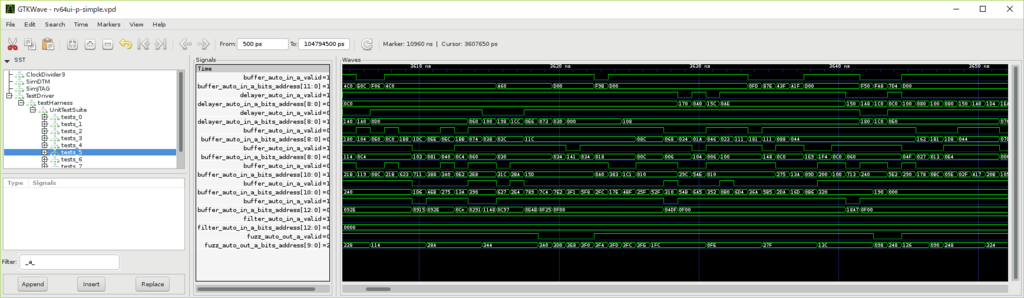

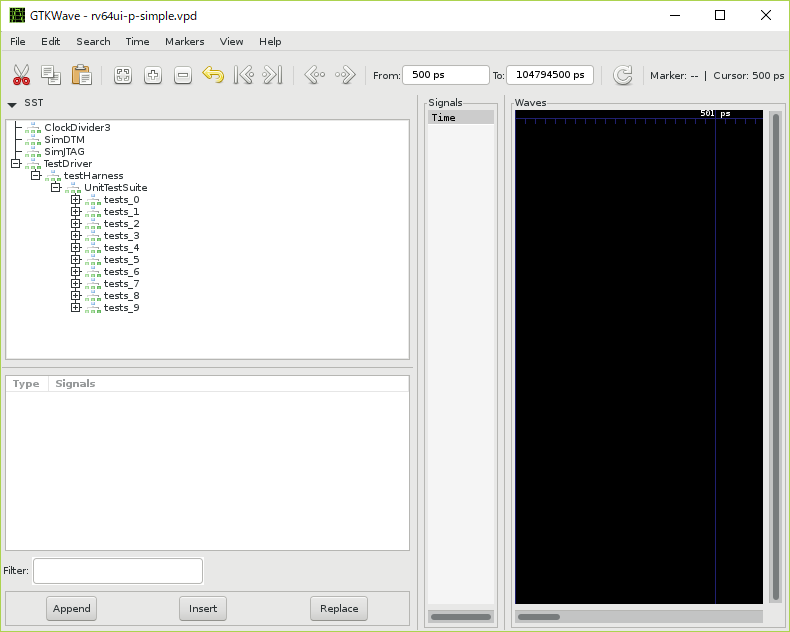

波形を開いてみるとこのようになった。

それぞれで独立してテストを実施している。