試しに、RISC-V on Parallela ボードのRISC-Vデザインをビルドしてみた。

リポジトリは以下に存在している。

https://github.com/eliaskousk/parallella-riscv

ここでは、Vivadoを用いて合成するので、LinuxマシンにVivadoがインストールされているのが前提だ。

まずはデザインをcloneしてくる。

git clone https://github.com/eliaskousk/parallella-riscv.git

以降で、必要なsubmodulesはビルドスクリプトが勝手にフェッチしてくるので問題ない。

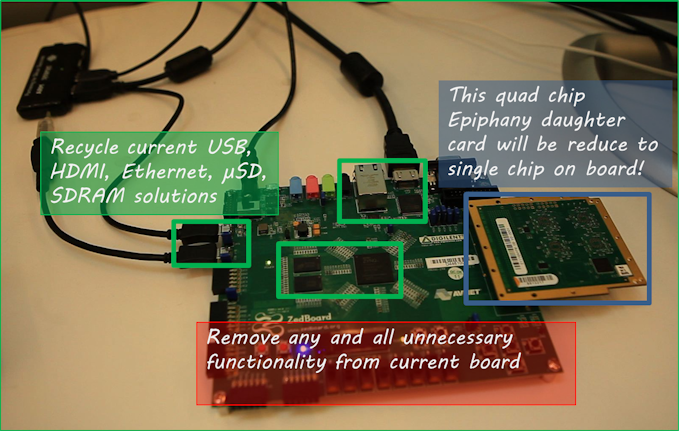

コンフィグレーションの変更を行う。今回は、RISC-VをZedBoardで動かしたいのと、Vivadoを2016.4で動作させるので、以下のような変更を行う。

diff --git a/scripts/settings.sh b/scripts/settings.sh

index 7f7dca2..e651f48 100644

--- a/scripts/settings.sh

+++ b/scripts/settings.sh

@@ -1,10 +1,10 @@

#!/bin/bash

-BOARD=parallella

+BOARD=zedboard

export BOARD

echo "\$BOARD set to ${BOARD}"

-JOBS=8

+JOBS=4

export JOBS

echo "\$JOBS set to ${JOBS}"

@@ -12,7 +12,7 @@ VIVADO_PATH=/opt/Xilinx/Vivado

export VIVADO_PATH

echo "Vivado path set to ${VIVADO_PATH}"

-VIVADO_VERSION=2015.4

+VIVADO_VERSION=2016.4

export VIVADO_VERSION

echo "Vivado version set to ${VIVADO_VERSION}"

次に、ホストのソフトウェアをビルドする。もしかしたらこれは必要ないかもしれない。

sudo apt install openssl-dev

./scripts/build.host.software.sh

RISC-Vデザインのビルドを行う。Vivadoが立ち上がり、合成が始まる。

./scripts/build.host.software.sh

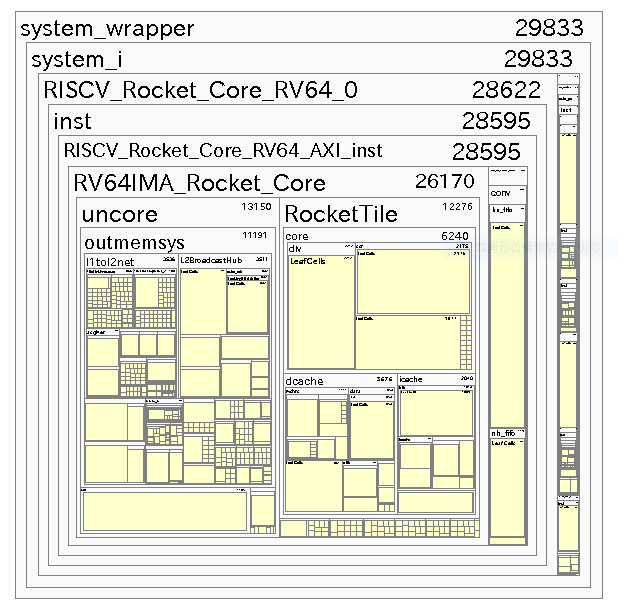

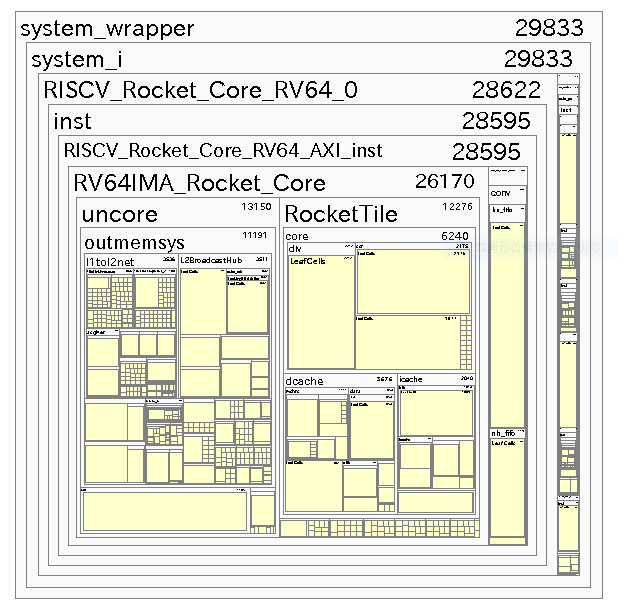

しばらく待っているとビルドが終了するので、dcp(design check point)のファイルを読み込んで何がどうなっているのか確認してみよう。

vivado ./zedboard/fpga/zedboard_riscv/system.runs/impl_1/system_wrapper_opt.dcp

当たり前だがほとんどがRISC-Vのデザインとなり、いくつかAXIのインタフェースを備えている。