NVDLAというか、畳み込み演算をどのようにハードウェアで実現するかということをさらに掘り下げている。

- NVDLA : Unit Description

Unit Description — NVDLA Documentation

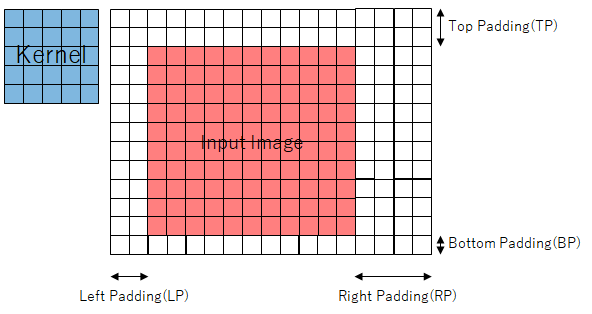

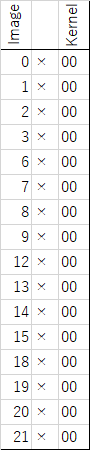

NVDLAのConvolution DMAは、以下のような画像に対して入力画像とカーネルを畳み込むことを考える。ここではチャネルについては無視している。

上記の図における、各パラメータは以下の通りである。

- Top Padding(TP) : 画像データに対して上部に何ピクセルパディングを入れるか。

- Bottom Padding(BP) : 画像データに対して下部に何ピクセルパディングを入れるか。

- Left Padding(LP) : 画像データに対して左部に何ピクセルパディングを入れるか。

- Right Padding(RP) : 画像データに対して右部に何ピクセルパディングを入れるか。

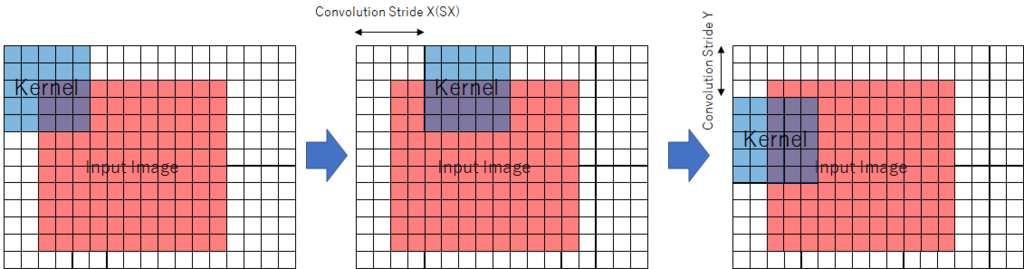

これに対して、カーネルの畳み込みを行うと以下のようになる。ここでと

は畳み込みのストライド数である。

それぞれ

、

として表現している。

というのは畳み込み後の画像のサイズであるが、これを以下のように表現している。

ただし、

畳み込みをしていくのは以下のようなイメージだ。ここではX方向のストライド数=4, Y方向のストライド数=3としている。

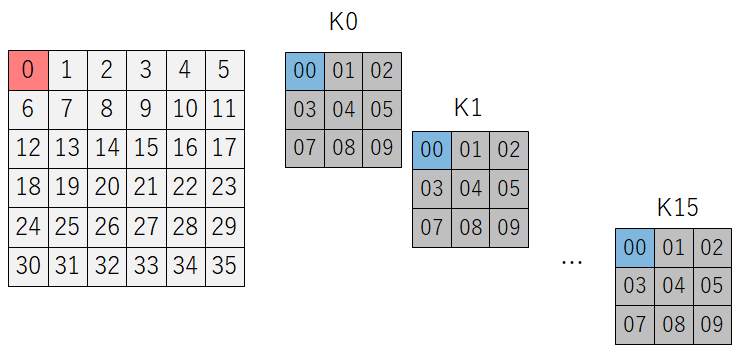

NVDLAにおける畳み込み演算

NVDLAにおけるアトミック操作

アトミック操作は重みカーネルの1ドットに対して掛け算を実施する計算に相当する。

これは以下の計算をしていることに相当する。

[0] × [00](K0)[0] × [00](K1)[0] × [00](K2)[0] × [00](K3)- …

[0] × [00](K15)

ここでは、カーネルの数を1として考えてみる。そうすると、上記の図における画像の座標0と、カーネルの座標00の乗算を行っていることに相当する。

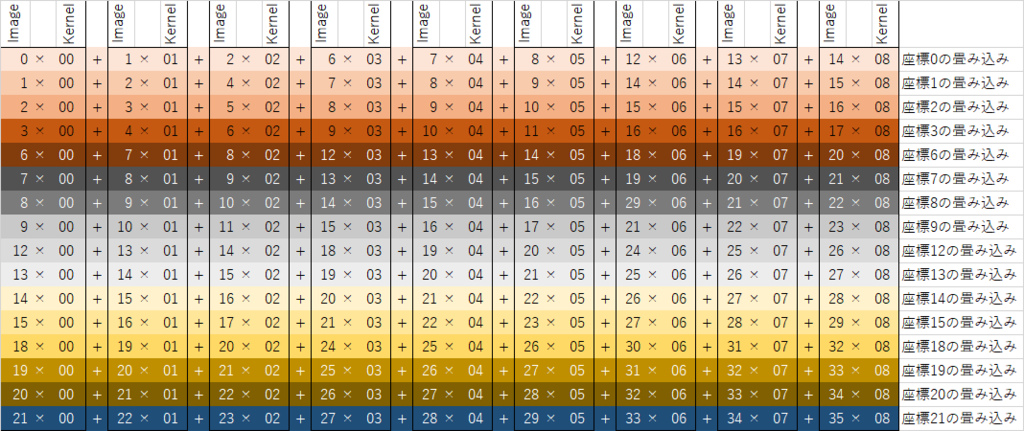

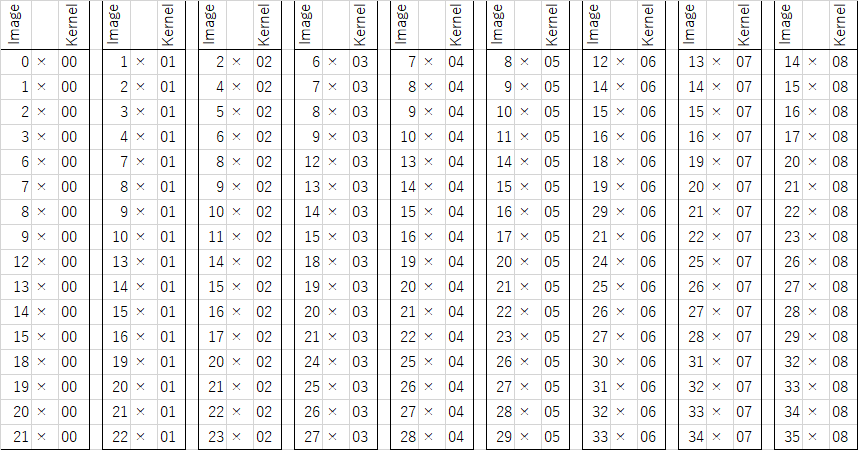

NVDLAにおけるストライプ操作

ストライプ操作は、上記のアトミック操作を連続して実行することに相当する。カーネルの位置は変えずに、入力画像の位置をずらす。

先ほどの式を拡張して考えると、上記の図における画像の座標0から座標21までの四角形の16要素と、カーネルの座標00の乗算を行っていることに相当する。

NVDLAにおけるブロック操作

ブロック操作は、上記のブロック操作をさらに連続して実行する。画像の位置と、カーネルの位置を変えながら演算を行う。カーネルのサイズはなので、画像の位置を0,1, 2, 6, 7, 8, 12, 13, 14とずらす。

一方でカーネルの位置も、00, 01, 02, ... 08 までずらす。

先ほどの式を拡張して考えると以下のような演算を実行している。

最終的な畳み込みは以下のように行方向に加算することで計算できる。