自作RISC-Vシミュレータがある程度落ち着いてきたので、キリがいいところでGitHubで公開することにした。

まあSpike(riscv-isa-sim)の劣化Cloneだと言ってしまえばそれまでなので、あまり意味はないのだけれど。。。

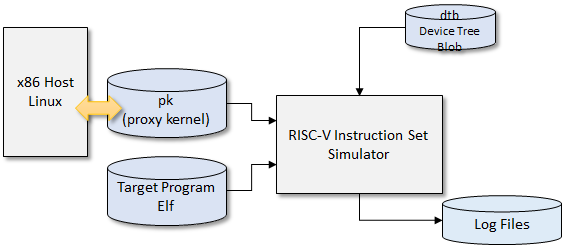

図. 自作RISC-Vシミュレータの外部インタフェース

使い方はGitHub上のREADME.mdに書いてある。BSDライセンスなので自由に改造してやってください。 まあこういうツールの場合BSDライセンスが良いのかどうかもよく変わっていないけれども? RISC-Vの精神に基づいてみた。

Spikeシミュレータとの差分点としては、デバッグ情報がしっかり出力できるようにした。レジスタアクセス情報からメモリアクセスの情報まで、--debugオプションによりしっかり情報を出力する。

その影響で--debugオプションをかなり遅くなってしまうのだが、それは今後の改善ということにする。

あとは関数トレースといって、関数Callのツリーを生成できるようになっている。--trace-hierにより生成できる。

テストパタンのPass状況だが、402本中まだ10本は取っていないんだな。。。 これはCompressed命令がモードによって少し細かい動きがある影響。 この辺は命令デコーダの自動生成スクリプトを改良する必要がある。

という訳で、RISC-Vに興味がある限りはメンテナンスをしていくつもり。 将来RISC-Vの実装を作ることになったら、検証用のシミュレータとして使っていきたいかも。