以下の記事の続き。仕様書を読んでいく。サイトとかPIPの定義、制約について細かく書いてあるが、正直この段階では何を言っているのか良く分からない。

fpga-interchange-schema.readthedocs.io

FPGA Interchange Document

Cell, BEL, サイトの設計

FPGA interchangeデバイスリソースのカギとなるコンポーネントの一つは、セルライブラリの関係性とデバイスのBELとサイトの定義である。良く設計されたセルライブラリとフレキシブルかつ簡潔なBELとサイトの定義はハードウェアの効率的な配置配線が可能となる。

良い設計は捉えることが難しいが、ドキュメントによりいくつかの考慮について語ることは出来る。

セルの配置とBELピンのドライバに関する仮定

重要な注意点として、BELはセルの配置可能な場所を表し、BELには1つのセルをマッピングすることになる。つまり、セルライブラリの設計とBELの設計が、配置配線ツールで表現可能な内容に強く影響するということになる。

セルライブラリの粒度

ここでいうセルというのは、用語の定義上LUT4などのBELの要素であると考えることができる。

LUT4はLUT3のエレメントを2つ接続したものであるが、もし内部のMUX(2つのLUT3を接続しているもの)にアクセスすることができなければ、これらの要素を公開すること自体にあまり意味はない。

セル定義は、合成がマッピングできる程度に詳細であるべきであるが、配置配線ツールがほとんど選択しないほど詳細であってはならない。もし、そのセルが1つしか合法的な配置がない場合、その価値は相対的に低くなる。

サイト境界の記述

新しいファブリック用のFPGAインターチェンジデバイスを設計する際、重要な検討事項の1つが、サイトの境界をどこに引くかということになる。これはファンアウトによるローカル配線の混雑度に直接影響する。内部スタティックルーティングのMUXおよび出力MUXは、それを駆動するBELの可能数よりもかなり少ない信号を収容できる可能性がある。その場合、クラスタ化するアプローチではパッキングする最中に、非クラスタ化するアプローチでは配置中に、ローカルな輻輳を解決できるように、サイト境界を十分に大きく書いて、これらのケースを補足することが重要である。いずれの場合も、配置に強く依存する局所的な混雑は、配置とルーティングを融合したアルゴリズムを使用しない限り、一般的なルーティングの前に解決する必要がある。

FF制御集合のルーティング

一般的なケースとして、SRタイプ信号やCEタイプ信号などのFFコントロールセットが検討される。ほとんどのファブリックSLICEタイプでは、SRとCE の制御信号はSLICEの複数の列で共有される。これはローカルサイトの混雑の一般的な例で、上述の理由からサイトの境界はこのようなロ ーカル配線を共有するすべてのBELを包含してい る 必要がある。

制御信号に関するもう一つの考慮点は、ローカルルーティング輻輳として表現できない制御信号制約の存在である。たとえば、SR制御線がセットかリセットか(または非同期セットか非同期リセットか)をBELのセットが共有している場合、サイト境界を拡張して、これらの暗黙の構成を共有するBELをカバーすることが一般的である。デバイスリソース内の制約システムは、このような非ルーティング駆動のコンフィギュレーションを処理するように設計されています。

BEL境界の記述

BELの定義には、ファブリックのプリミティブエレメントの周りに境界を作ることが必要となる。その境界をどこに設定するかは、FPGAインターチェンジのセルライブラリの設計に強い影響を与える。

例えば、スタティックルーティングのMuxをBELの外に置いた場合、配置配線ツールがサイトの子雑を解決するのに使用することができるが、逆に言おうと合成時の複雑性が増加する。

スタティック配線MuxがBELに統合される最も一般的なケースは、BRAMとFIFOのアドレスと配線のコンフィギュレーションである。合成時にアドレスとデータ幅を選択するが、これはセル上のパラメータとしてエンコードされます。通常、配置配線ツールは、これらのスタティック配線マルチプレクサのコンフィギュレーションについて意味のある選択を行わないが、ハードウェアには存在する。

静的ルーティングMuxとビットストリームフォーマット

スタティックルーティングのMUX を含むか含まないかのBEL境界を引く際に念頭に置くべき事は、 その下のビットストリームに存在する設定可能性の度合いです。一部のスタティック配線Muxはビ ットストリーム内のコンフィギュレーションビットを共有してい るため、2 つの異な るスタティック配線Muxとして表現すると、配置配線ツールで表現で きない柔軟性をもたらすでしょう。これにより、ビットストリームに変換できない物理的なネットリストが生じる可能性があります。

これは、セルとBELライブラ リの緊密な結合によって対処できる場合があります。このアイデアは、不正なスタティックルーティングMUXコンフィギュレーションを避けるために、セルポートとBELピンのマッピングを制限することです。このアプローチには限界があります。一般に、BEL の境界を描く 際には、ビットストリームがスタティック配線Muxをどのように表現するかを考慮する必要があります。

Stratix IIとStratix 10 ALM

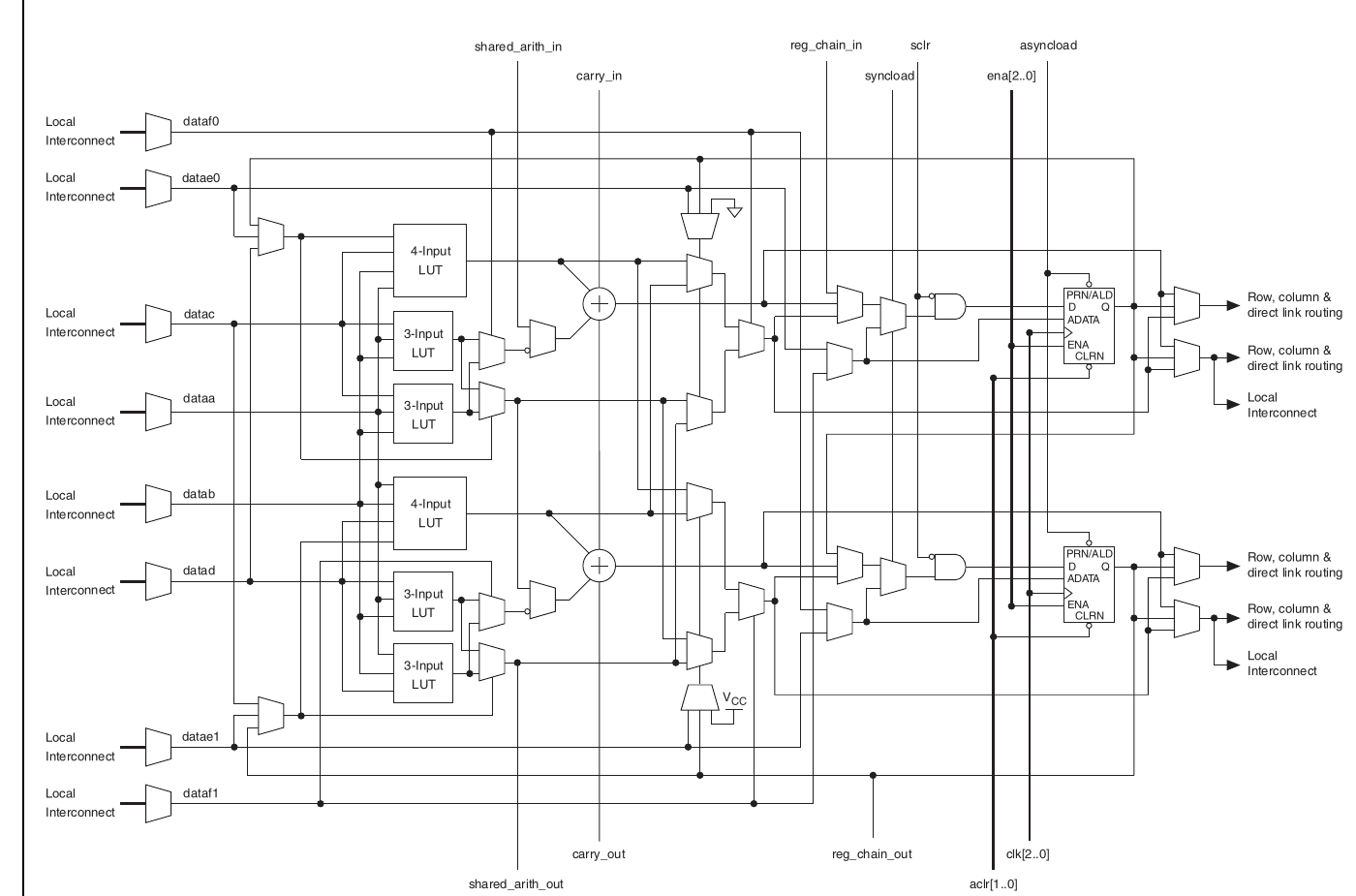

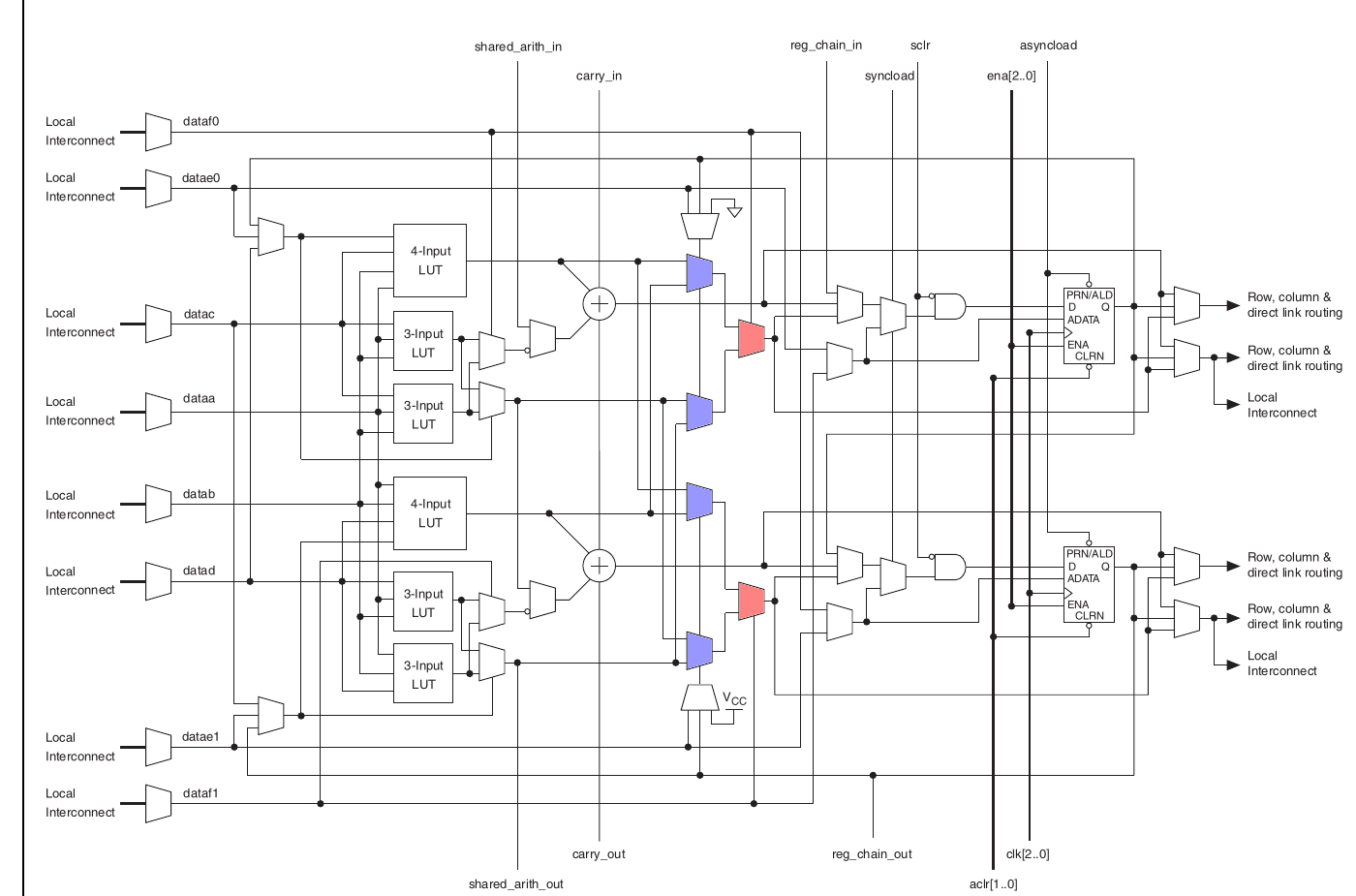

- Stratix II のスライス

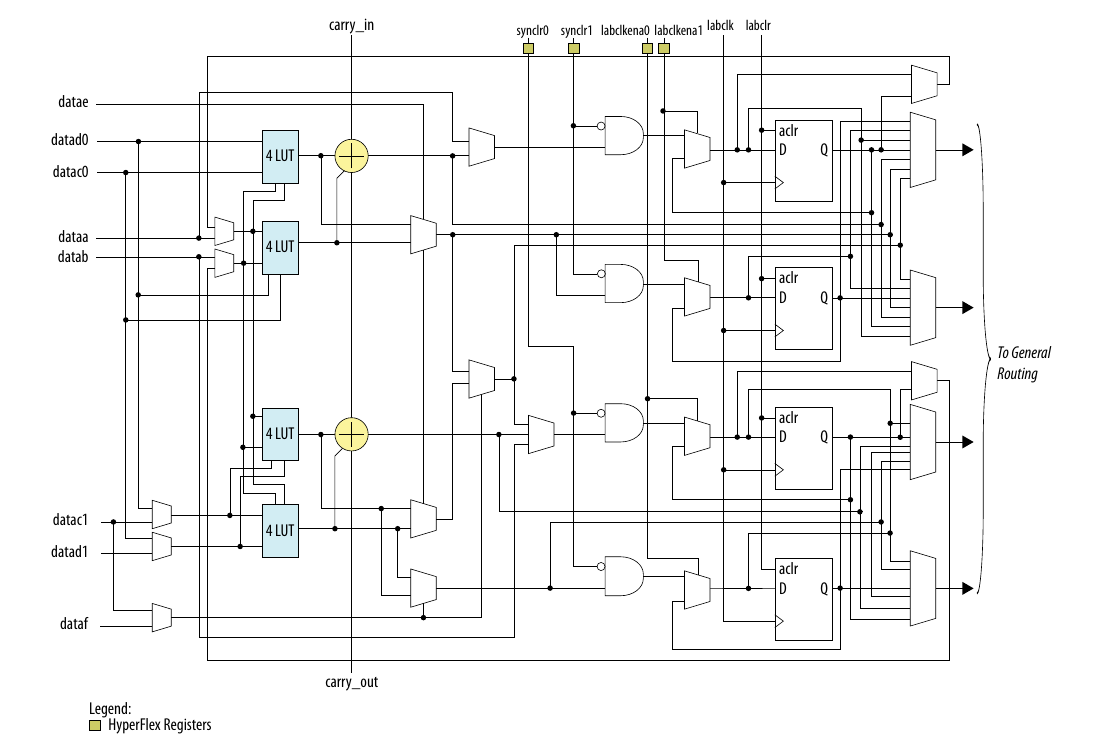

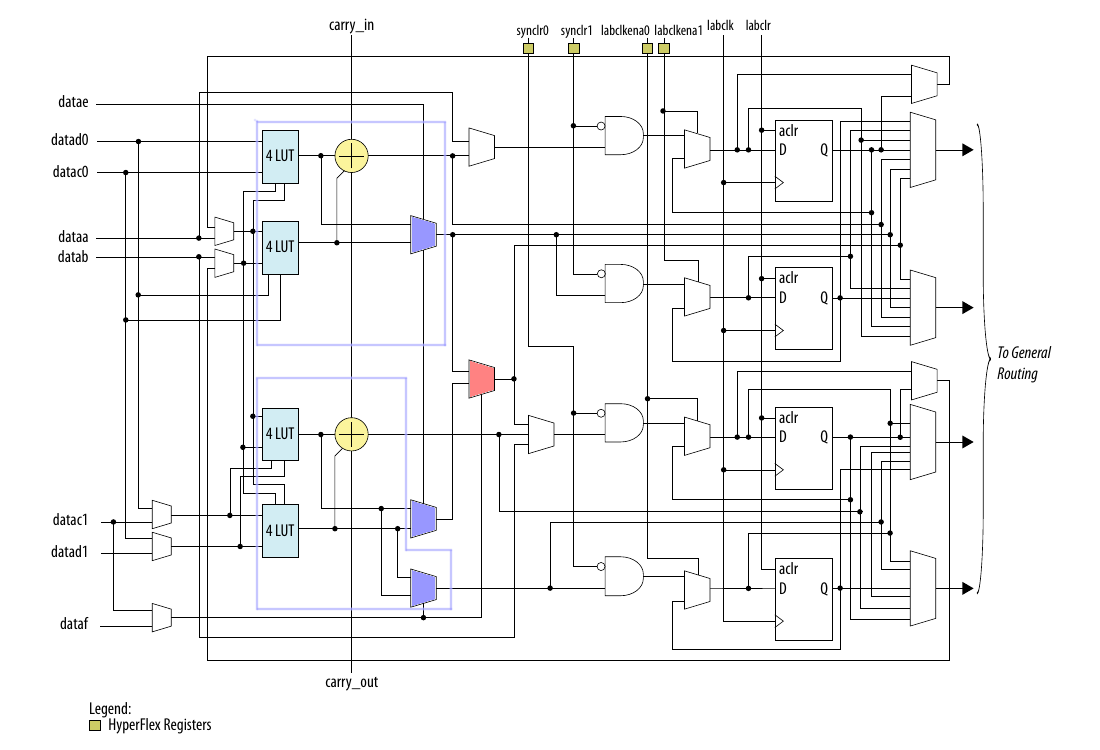

- Stratix 10のスライス

どちらのFPGAも、基本的には4-LUTを4つ並べて表現されている。

Stratix IIの場合には3LUTを2つ並べてそれを選択する論理が存在している。これは実質的に2つのLUT4エレメントであり、出力ラインは独立である。

Stratix 10ではLUT4のエレメントは使用されているが、上位の選択線は削除されている。

従って、Stratix IIの4LUTのエレメントのが4つ出力されていると考えることができる。いくつかのLUT4の出力はキャリーエレメントに接続されているため、配置配線ツールは直接接続するためにLUT4もしくはそれ以下への配置を行うことが可能となる。しかし出力がキャリーエレメントによって使用されない場合、Stratix IIはMUXF5(以下の青いエレメント)およびMUXF6(赤いエレメント)によって接続される。

従ってStratix IIのサイトレイアウトでは、以下のBELが必要となる:

- LUT4のBELを4つ、キャリーに接続されているもの。

- LUT6のBELを2つ。FFもしくは出力MUXに接続されるもの。

Stratix 10のサイトレイアウトでは、LUT4のエレメントが直接キャリーに接続されているのは同様である。Stratix 10のサイトではLUT5として使用される出力ポートが用意されている。以下の図ではLUT5は青のぼっくで表現されており、LUT6は赤のボックスで表現されている。

従ってStraix 10のサイトレイアウトでは、以下のBELが必要となる。

- LUT4のBELを4つ、キャリーに接続されているもの

- LUT5のBELを2つ、出力FFもしくは出力MUXに直接接続されているもの

- LUT6のBELを1つ、出力FFもしくは出力MUXに直接接続されているもの