RISC-V Day Tokyo 2018にも出てきたハイパーバイザ仕様、はっきり言って自分にはさっぱり理解できなかった。 そもそもハイパーバイザの知識が無さすぎるので、これが良い機会なので一から勉強してみることにする。

参考にしているのは、 RISC-V ISA Manualの最新版(正式リリース版ではなくDraft版。こちらにはハイパーバイザの仕様案が含まれている)。

また、RISC-VのSBI(Supervisor Binary Interface)については以下を参考にする。こちらも時間を見つけて読み込んでいく。

以下の文章はRISC-V ISA Manual Draft をベースにしていますが、直訳ではありません。 また、ブログ著者の知識不足のため多分に間違いが入っている可能性があります。 間違いを見つけましたらご指摘いただけますとうれしく思います。

まだ途中だけれど、追記もしくは別のエントリ作成予定。

ハイパーバイザ拡張, Version 0.2-draft

Type-1とType-2のハイパーバイザをサポートするための命令セット仕様。

- Type-1のハイパーバイザとは

ハイパーバイザがハードウェア上で直接動作し、全てのOS(ゲストOS)はそのハイパーバイザ上で動作する方式を指す。狭義の「ハイパーバイザ」はこちらのみを指す。

- Type-2のハイパーバイザとは

ハードウェア上でまず別のOSが稼働し(このOSをホストOSと呼ぶ)、その上でハイパーバイザが(ホストOSのアプリケーションとして)稼働し、更にはハイパーバイザの上で更に別のOS(このOSをゲストOSと呼ぶ)を稼働させる方法である。狭義においては、Type 2はハイパーバイザには含まれない。

RISC-V のハイパーバイザ

ハイパーバイザの構成

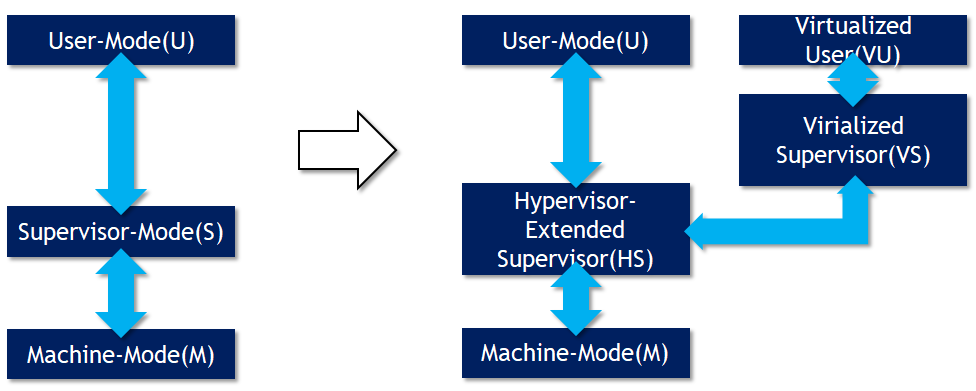

ハイパーバイザがサポートされている場合、RISC-Vのスーパバイザモードは、

- Hypervisor-extended Supervisor Mode(HS-Modeもしくは単純にハイパーバイザモード)

となる。

また、ハイパーバイザ拡張のために、"Guest Physical Address"から、スーパーバイザ物理アドレスへの変換機構が新たに定義される。

HS-ModeはS-Modeと同様の動作をするが、HS-Modeでの命令動作とCSRは上記のアドレス変換を行うことにより、ゲストOSを仮想S-Mode(VS-Mode)で動作するように制御が行われる。

通常のオペレーティングシステムはS-Modeで動作するようになっているが、HS-ModeとVS-Modeは同様に動作できるように定義される。

HS-Modeでは、OSもしくはハイパーバイザはRISC-VのSBI(Supervisor Binary Interface)を用いて互いに制御が行われる。HS-ModeのハイパーバイザはVS-ModeのゲストのためにSBIが実装されていることが想定されている。

ハイパーバイザサポート時のmisaレジスタ

ハイパーバイザが実装されている場合、CSRのmisaレジスタの7ビット目が1に設定される。また、ハイパーバイザが実装されている実装でも、misaの7ビット目をハードウェア的に0に設定されることは推奨されず、無効にできるようにすべきである。

※注釈1. Privileged Architectureはクラシックな仮想化の技術、つまりゲストOSがユーザレベルで動作し、いくつかのPrivileged命令が実行されると簡単に例外が検出できる、という構成に対して設計されている。ハイパーバイザ拡張は、これらの頻発される例外にを削減して、性能を向上させるために設計されている。

※注釈2. ハイパーバイザ拡張は、ハイパーバイザ拡張が実装されていないプラットフォームでも、この拡張を効率的にエミュレートできるように実装されている。つまり、ハイパーバイザがSモードで実行されて、ハイパーバイザのCSRへのアクセスにより例外が発生してM-Modeに移行し、Shadow Page Tableを管理する必要になる場合である。Type-2ハイパーバイザのCSRアクセスの大半はS-Modeでも違反ではなく、したがって例外は発生しない。ハイパーバイザは同様にネストされた仮想化にも対応できる。

5.1 ハイパーバイザ

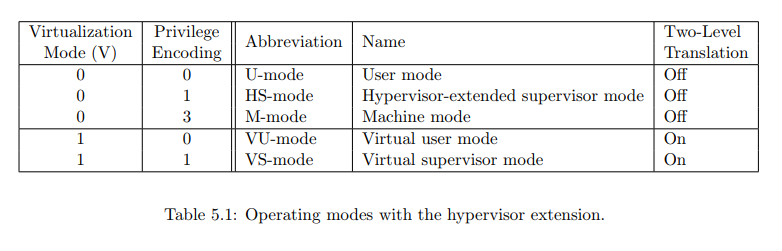

仮想モード(Virtualization Mode, Vビット)により、現在のHartがゲストとして実行されているのかどうかを判定する。

- V=1 : 仮想S-Mode(VS-Mode), 仮想U-Mode(VU-Mode)で動作している。これはゲストOS上で動作していることを意味する。また、V=1の場合は2レベルアドレス変換が有効である。

- V=0 : M-Mode, HS-Mode, HS-Mode下のOS上で動作しているU-Modeのどれかである。

5.2 ハイパーバイザCSR

ハイパーバイザにおけるバックグラウンドCSR、フォアグラウンドCSRの役割

HS-Mode上で動作するOSとハイパーバイザは、例外と割り込み、アドレス変換を処理するためにスーパバイザCSRを使用する。CSRはHS-Modeモード上で実装されており、VS-Modeで実装されていない。しかし、VS-Modeの2レベルアドレス変換と動作の制御を管理するために使用させる。これらは、hstatus, hedeleg, hideleg, hgatpとする。

「バックグラウンド」のスーパバイザCSRは、いくつかの存在している「フェアグラウンド」スーパバイザのコピーである。例えば、bsstatusCSRはsstatusのコピーである。仮想モードが切り替わるとき、バックグラウンドのスーパバイザCSRとフォアグラウンドのCSRをスワップする。

- V=0

- V=1

HS-mode時のXLENのことをHSXLENと呼ぶ。

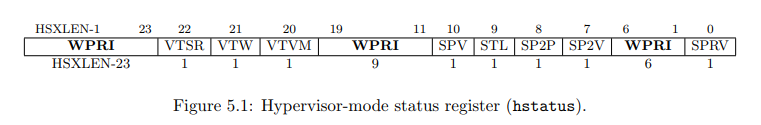

5.2.1 Hypervisor Status Register (hstatus)

mstatusレジスタと同様のレジスタであり、VS-modeのゲストの例外動作について記録している。

各ビットの役割

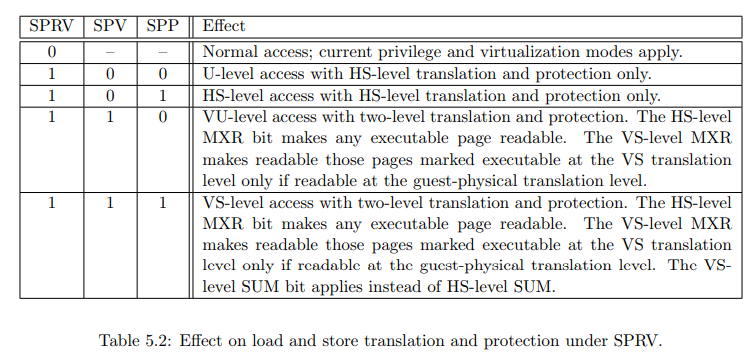

VTSR / VTW, VTVMビット :mstatusと同様だが、V=1の時に、RSET,WFI命令で使用される。SPV(Supervisor Previous Virtualization Mode)ビット : 例外が発生したときにの、仮想モードの情報を記録する。V=0時にSRET命令が実行されると、SPVにVが設定される。HS-mode時に例外が発生すると、例外が発生する前にSP2VとSP2PにSPVとHSレベルのSPPの値が設定される(例外の前に、HSレベルのSPPはV=0時には

sstatus.SPPであり、V=1時にはbssatus.SPPである)。V=0のときにSRET命令が実行されると、逆の操作が行われる: つまり、SPVとsstatus.SPPが新しい仮想モードの例外モードに設定される:つまり、それぞれの値はSP2V, SP2Pに書き込まれる。STL(Supervisor Translation Level)はメモリアクセス失敗、ページ例外時のアドレス変換レベルを示している。HS-modeで例外が発生した場合には必ず設定される。- SPRVビット

- SPRV=0の場合 : メモリアクセス・プロテクションは通常通り行われる。

- SPRV=1の場合 : ロード・ストアメモリアクセスは、現在の仮想モードがhstatus.SPVとして扱われ、現在の特権モードがHSレベルのSPPとして扱われる(V=0の場合は

sstatus.SPPが使用され、V=1の場合はbsstatus.SPPとなる)。