AWS F1インスタンス HDK の勉強を続けている。 前回ModelSimを使ってcl_dram_dma の波形パタンを取得しようとしたが、動作が非常に遅くなってしまい失敗した。

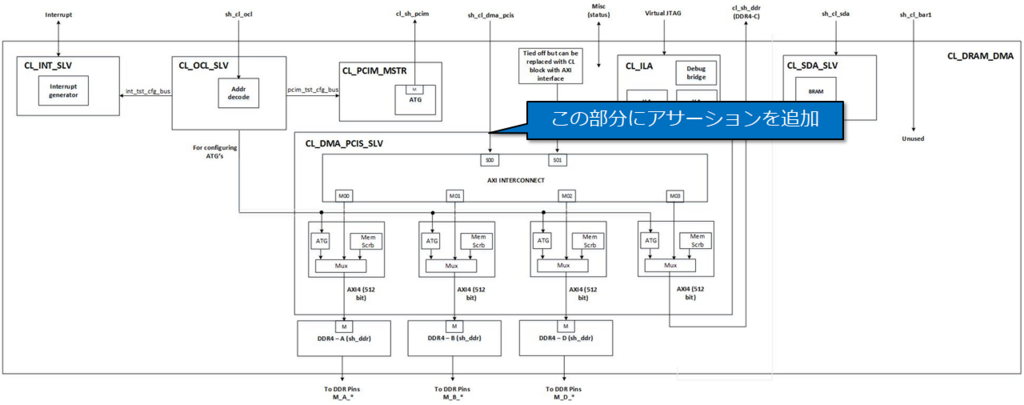

どうにかして波形以外の情報を取得するためには、アサーションのようなものを組み込んでテキストファイルとしてログを取得するしかない。

という訳で、cl_dram_dmaのAXIバスの位置にロガーを挿入して動作を確認してみた。 GitHubに変更箇所をアップロードしてある。

ちなみに、テストパタンはTBで記述されている。ソフトウェアで書いてあるのかと思ったら違うのね。

aws-fpga/hdk/cl/examples/cl_dram_dma/verif/tests/test_dram_dma.sv

0x0000_0000_0002 から 128byte ほど 0xAA を転送する。

//Queue data to be transfered to CL DDR tb.que_buffer_to_cl(.chan(0), .src_addr(host_memory_buffer_address), .cl_addr(64'h0000_0000_0002), .len(len0) ); // move buffer to DDR 0 // Put test pattern in host memory for (int i = 0 ; i < len0 ; i++) begin tb.hm_put_byte(.addr(host_memory_buffer_address), .d(8'hAA)); host_memory_buffer_address++; end

- 0x0004_0000_0000 から 128byte ほど 0xBB を転送する。

tb.que_buffer_to_cl(.chan(1), .src_addr(host_memory_buffer_address), .cl_addr(64'h0004_0000_0000), .len(len1) ); // move buffer to DDR 1 for (int i = 0 ; i < len1 ; i++) begin tb.hm_put_byte(.addr(host_memory_buffer_address), .d(8'hBB)); host_memory_buffer_address++; end

- 0x0008_0000_0005 から 6000byte ほど 0xCC を転送する。

tb.que_buffer_to_cl(.chan(2), .src_addr(host_memory_buffer_address), .cl_addr(64'h0008_0000_0005), .len(len2) ); // move buffer to DDR 2 for (int i = 0 ; i < len2 ; i++) begin tb.hm_put_byte(.addr(host_memory_buffer_address), .d(8'hCC)); host_memory_buffer_address++; end

- 0x000C_0000_0000 から 300byte ほど 0xDD を転送する。

tb.que_buffer_to_cl(.chan(3), .src_addr(host_memory_buffer_address), .cl_addr(64'h000C_0000_0000), .len(len3) ); // move buffer to DDR 3

for (int i = 0 ; i < len3 ; i++) begin

tb.hm_put_byte(.addr(host_memory_buffer_address), .d(8'hDD));

host_memory_buffer_address++;

end

一応、正しくログが取れているようだ。

tb.card.u_ddr4_rdimm_D.rcd_enabled.genblk1.u_ddr4_dimm.rank_instances[0].even_ranks.u_ddr4_rank.Micron_model.instance_of_sdram_devices[15].micron_mem_model.u_ddr4_model.always_diff_ck.if_diff_ck:Initialization complete @27185552

tb.card.u_ddr4_rdimm_D.rcd_enabled.genblk1.u_ddr4_dimm.rank_instances[0].even_ranks.u_ddr4_rank.Micron_model.instance_of_sdram_devices[16].micron_mem_model.u_ddr4_model.always_diff_ck.if_diff_ck:Initialization complete @27185552

tb.card.u_ddr4_rdimm_D.rcd_enabled.genblk1.u_ddr4_dimm.rank_instances[0].even_ranks.u_ddr4_rank.Micron_model.instance_of_sdram_devices[17].micron_mem_model.u_ddr4_model.always_diff_ck.if_diff_ck:Initialization complete @27185552

[ 33462000] : Initializing buffers

[ 33462000] : starting H2C DMA channels

33474000 : [sh_cl_dma AW] LEN= 0 SIZE=6 ADDR=0000000000000002

33474000 : [sh_cl_dma W] STB=fffffffffffffffc DATA=aaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa0000

33482000 : [sh_cl_dma W] STB=ffffffffffffffff DATA=aaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaaa

33490000 : [sh_cl_dma AW] LEN= 0 SIZE=6 ADDR=0000000000000040

33494000 : [sh_cl_dma W] STB=0000000000000003 DATA=0000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000000aaaa

33506000 : [sh_cl_dma AW] LEN= 0 SIZE=6 ADDR=0000000000000080

33510000 : [sh_cl_dma W] STB=ffffffffffffffff DATA=bbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbb

33522000 : [sh_cl_dma AW] LEN= 1 SIZE=6 ADDR=0000000400000000

33526000 : [sh_cl_dma W] STB=ffffffffffffffff DATA=bbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbbb

33642000 : [sh_cl_dma AW] LEN= 0 SIZE=6 ADDR=0000000800000005

33646000 : [sh_cl_dma W] STB=ffffffffffffffe0 DATA=cccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccc0000000000

33650000 : [sh_cl_dma W] STB=ffffffffffffffff DATA=cccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccccc

33766000 : [sh_cl_dma AW] LEN= 62 SIZE=6 ADDR=0000000800000040

...