LiteXのLiteScopeではどうにも細かい信号を取得することができないので、Xilinxの純正の波形のデバッグツールであるILA(Integrated Logic Analyzer)を使って内部の信号を観察する方法を見てみる。

まず、ILA無しでLiteXでFPGAをビット・ストリームファイルを作成するのは、以下のコマンドを実行すればよいだろう。

python3 -m litex_boards.targets.digilent_nexys_video --cpu-type=vexriscv --build --output-dir vexriscv_build

この時、vexriscv_build/gatewareにVivadoを実行したtclファイルなどのログが残る。これを改造して、ILAを挿入する方法を試行していきたいと思う。

create_project -force -name digilent_nexys_video -part xc7a200t-sbg484-1

set_msg_config -id {Common 17-55} -new_severity {Warning}

...

基本的にこのコマンドを使えば、LiteXのFPGAビット・ファイルを再現できる。

vivado -source ./digilent_nexys_video.tcl -mode tcl

したがって、このdigilent_nexys_video.tclを改造して、ILAを挿入する。

簡単に言えば、以下のようなコマンドをファイル内に挿入する。

create_debug_core u_ila_0 ila

set_property C_DATA_DEPTH 1024 [get_debug_cores u_ila_0]

set_property C_TRIGIN_EN false [get_debug_cores u_ila_0]

set_property C_TRIGOUT_EN false [get_debug_cores u_ila_0]

set_property C_ADV_TRIGGER false [get_debug_cores u_ila_0]

set_property C_INPUT_PIPE_STAGES 0 [get_debug_cores u_ila_0]

set_property C_EN_STRG_QUAL false [get_debug_cores u_ila_0]

set_property ALL_PROBE_SAME_MU true [get_debug_cores u_ila_0]

set_property ALL_PROBE_SAME_MU_CNT 1 [get_debug_cores u_ila_0]

connect_debug_port u_ila_0/clk [get_nets [list sys_clk]]

set_property port_width 1 [get_debug_ports u_ila_0/probe0]

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe0]

connect_debug_port u_ila_0/probe0 [get_nets main_basesoc_dbus_ack]

set debug_nets [lsort -dictionary [get_nets -regexp main_basesoc_dbus_cyc.*]]

set new_port [create_debug_port u_ila_0 probe]

set_property port_width [llength $debug_nets] $new_port

set_property PROBE_TYPE DATA_AND_TRIGGER $new_port

connect_debug_port $new_port $debug_nets

ポイントは、get_netsによってプローブしたい信号を取得し、それを新たに作成したILAのデバッグポートにひたすらつないでいくことだ。

ある程度テンプレート化して、debug_netsで信号を取得したうえで数字順にソーティングするようにしている。

最後に、ltxファイルを出力してデバッグ用のファイルを書き出す。

write_bitstream -force digilent_nexys_video.bit

write_cfgmem -force -format bin -interface spix4 -size 16 -loadbit "up 0x0 digilent_nexys_video.bit" -file digilent_nexys_video.bin

write_debug_probes -force digilent_nexys_video.ltx

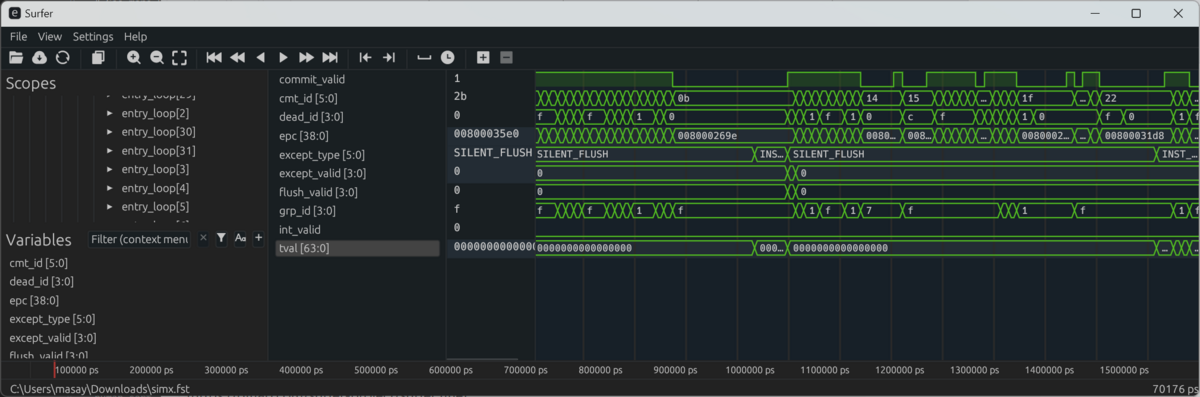

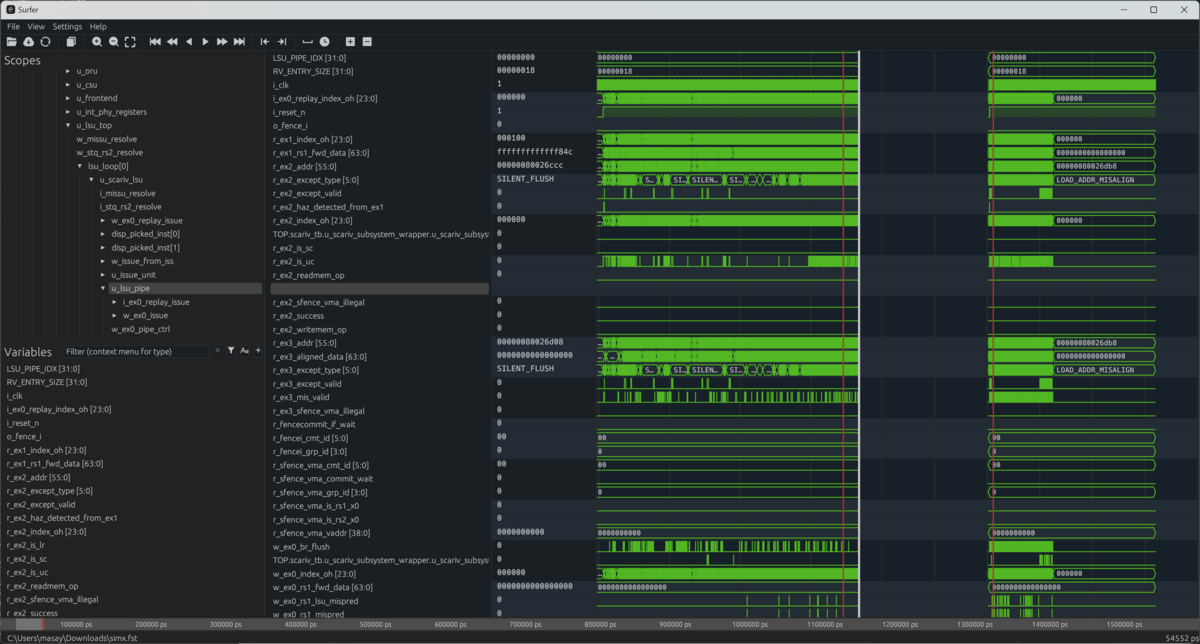

Vivado LabでFPGAに書き込みを行うと、ILAが立ち上がって、トリガによる実行が可能になる。

うーん、やっぱりLiteScopeより便利だ。