PLICの接続について、ひたすらバスをつなげて実装している。とりあえずコンパイルが通るようになったが、

まだシミュレーションが止まってしまうので、波形を見て要解析だな...

[serial2console] loaded (0x55e25615cef0)

[gmii_ethernet] loaded (0x55e25615cef0)

[ethernet] loaded (0x55e25615cef0)

[clocker] loaded

[xgmii_ethernet] loaded (0x55e25615cef0)

[serial2tcp] loaded (0x55e25615cef0)

[spdeeprom] loaded (addr = 0x0)

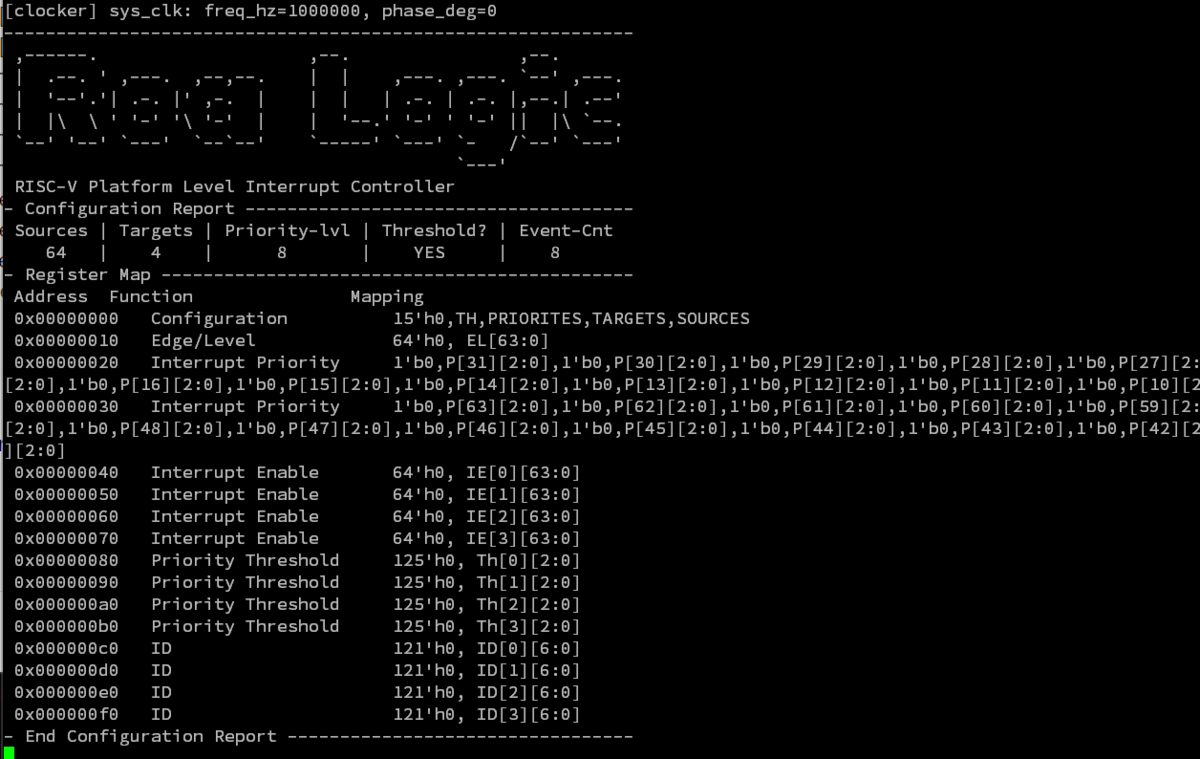

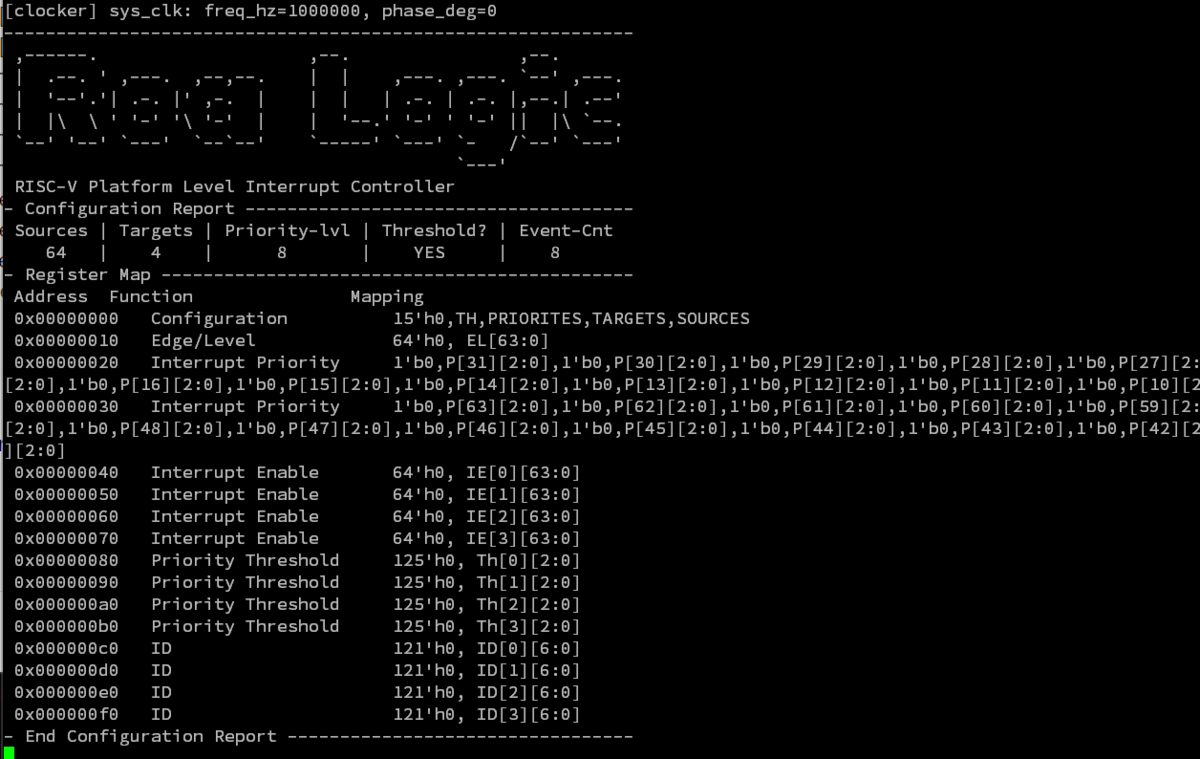

[clocker] sys_clk: freq_hz=1000000, phase_deg=0

------------------------------------------------------------

,------. ,--. ,--.

| .--. ' ,---. ,--,--. | | ,---. ,---. `--' ,---.

| '--'.'| .-. |' ,-. | | | | .-. | .-. |,--.| .--'

| |\ \ ' '-' '\ '-' | | '--.' '-' ' '-' || |\ `--.

`--' '--' `---' `--`--' `-----' `---' `- /`--' `---'

`---'

RISC-V Platform Level Interrupt Controller

- Configuration Report -------------------------------------

Sources | Targets | Priority-lvl | Threshold? | Event-Cnt

64 | 4 | 8 | YES | 8

- Register Map ---------------------------------------------

Address Function Mapping

0x00000000 Configuration 15'h0,TH,PRIORITES,TARGETS,SOURCES

0x00000010 Edge/Level 64'h0, EL[63:0]

0x00000020 Interrupt Priority 1'b0,P[31][2:0],1'b0,P[30][2:0],1'b0,P[29][2:0],1'b0,P[28][2:0],1'b0,P[27][2:0],1'b0,P[26][2:0],1'b0,P[25][2:0],1'b0,P[24][2:0],1'b0,P[23][2:0],1'b0,P[22][2:0],1'b0,P[21][2:0],1'b0,P[20][2:0],1'b0,P[19][2:0],1'b0,P[18][2:0],1'b0,P[17][2:0],1'b0,P[16][2:0],1'b0,P[15][2:0],1'b0,P[14][2:0],1'b0,P[13][2:0],1'b0,P[12][2:0],1'b0,P[11][2:0],1'b0,P[10][2:0],1'b0,P[9][2:0],1'b0,P[8][2:0],1'b0,P[7][2:0],1'b0,P[6][2:0],1'b0,P[5][2:0],1'b0,P[4][2:0],1'b0,P[3][2:0],1'b0,P[2][2:0],1'b0,P[1][2:0],1'b0,P[0][2:0]

0x00000030 Interrupt Priority 1'b0,P[63][2:0],1'b0,P[62][2:0],1'b0,P[61][2:0],1'b0,P[60][2:0],1'b0,P[59][2:0],1'b0,P[58][2:0],1'b0,P[57][2:0],1'b0,P[56][2:0],1'b0,P[55][2:0],1'b0,P[54][2:0],1'b0,P[53][2:0],1'b0,P[52][2:0],1'b0,P[51][2:0],1'b0,P[50][2:0],1'b0,P[49][2:0],1'b0,P[48][2:0],1'b0,P[47][2:0],1'b0,P[46][2:0],1'b0,P[45][2:0],1'b0,P[44][2:0],1'b0,P[43][2:0],1'b0,P[42][2:0],1'b0,P[41][2:0],1'b0,P[40][2:0],1'b0,P[39][2:0],1'b0,P[38][2:0],1'b0,P[37][2:0],1'b0,P[36][2:0],1'b0,P[35][2:0],1'b0,P[34][2:0],1'b0,P[33][2:0],1'b0,P[32][2:0]

0x00000040 Interrupt Enable 64'h0, IE[0][63:0]

0x00000050 Interrupt Enable 64'h0, IE[1][63:0]

0x00000060 Interrupt Enable 64'h0, IE[2][63:0]

0x00000070 Interrupt Enable 64'h0, IE[3][63:0]

0x00000080 Priority Threshold 125'h0, Th[0][2:0]

0x00000090 Priority Threshold 125'h0, Th[1][2:0]

0x000000a0 Priority Threshold 125'h0, Th[2][2:0]

0x000000b0 Priority Threshold 125'h0, Th[3][2:0]

0x000000c0 ID 121'h0, ID[0][6:0]

0x000000d0 ID 121'h0, ID[1][6:0]

0x000000e0 ID 121'h0, ID[2][6:0]

0x000000f0 ID 121'h0, ID[3][6:0]

- End Configuration Report ---------------------------------