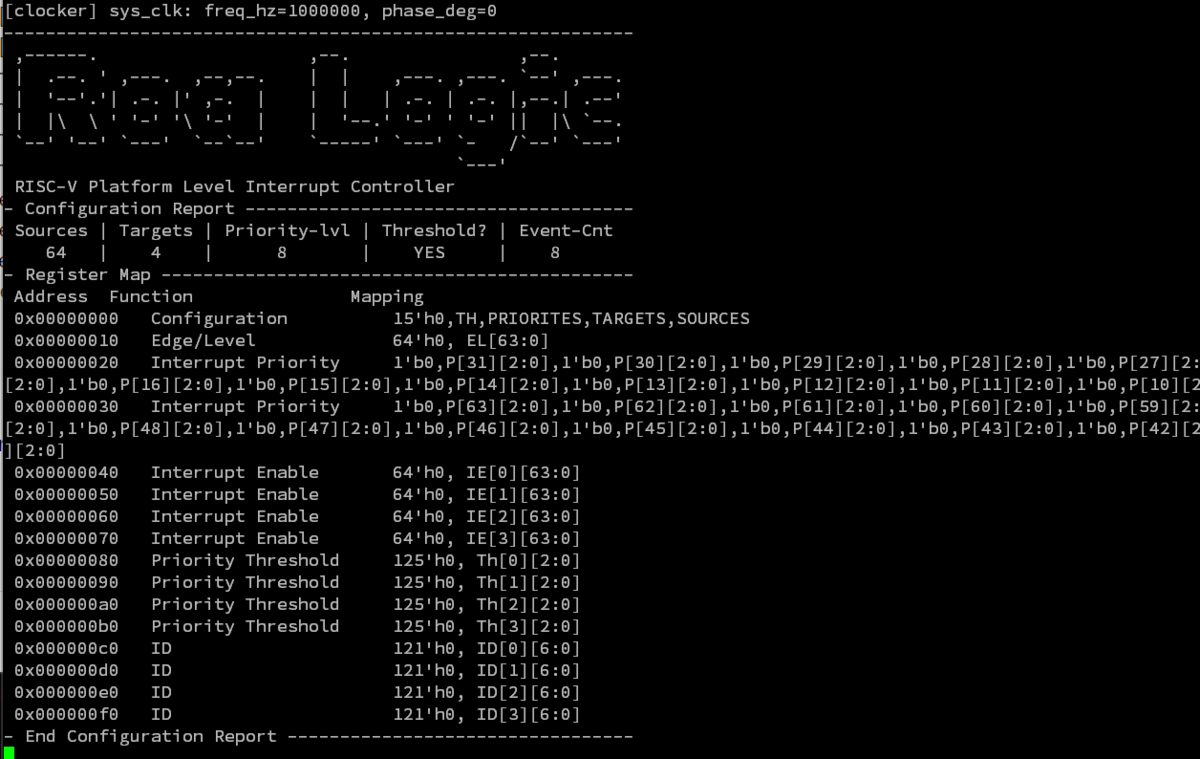

以下のPLICのオープンソース実装を使って自作CPUに接続していたのだが、どうもメモリマップが違う気がする。 かなり古い実装なので、現在の仕様と違うのはやむなしか...

なんか結局は自分で実装しなければならないような気がしているので、一生懸命仕様書を読んでいる。

割り込み

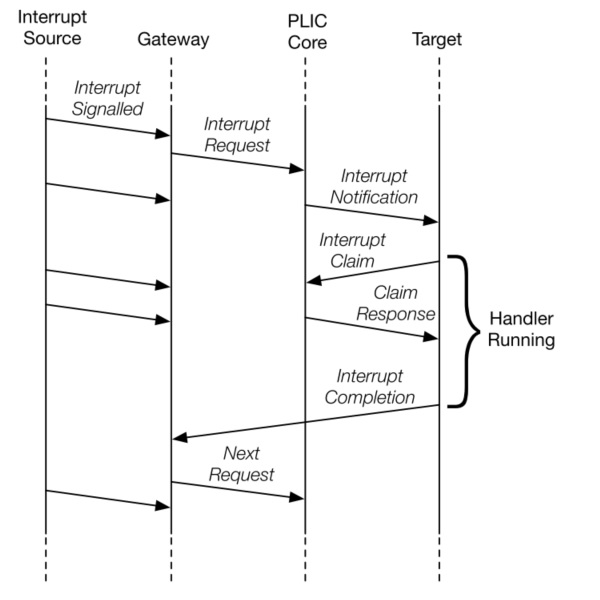

- 以下の図は、PLICを介して割り込みを処理するときにエージェント間を流れるメッセージを示している。

- グローバル割り込みは、各ソースから割り込みゲートウェイに送信される。

- 次に、割り込みゲートウェイは単一の割り込み要求をPLICコアに送信しし、コア割り込み保留中のビット(IP)を設定する。

- PLICコアは、Pending通知を1つ以上のターゲットに転送する。ターゲットには保留中のPendingが有効になっており、保留中のPendingにおける優先順位はターゲットごとのしきい値を超えている場合に送信される。

- ターゲットが外部割り込みを取得すると、割り込みClaimを送信する。最優先のグローバル割り込みの識別子を取得するように要求する。

- PLICコアは、対応する割り込みソースを保留中のビットをクリアする

- ターゲットが割り込みを処理した後、ゲートウェイはPending完了メッセージを送信する。

- 割り込みゲートウェイは初期状態に戻る。

- 割り込みゲートウェイ 割り込みの数だけ用意される。外部から割込みが挿入されると、それをレジスタに格納する。PLICのCompleteが入力されるとレジスタは解放される。 Completeが入力されるまでの間はInflightとなり、同じ割込みポートから新たな割り込みを挿入できない。