この記事は ハードウェア開発、CPUアーキテクチャ Advent Calendar 2016 - Qiita の19日目の記事です。

ハードウェア開発、CPUアーキテクチャ Advent Calendarも、25日分ほぼ埋まってきました。あともう少し、各担当者の皆様、頑張りましょう!

1. そもそも高位合成言語とは

ちまたでVerilog-HDL, VHDLの変わりになると流行っている高位合成言語だが、きちんとした定義はどのようになっているのだろう?

こちらの発表資料を見てみると、

- 今さら聞けない高位合成 ~1から学ぶ高位合成~

http://www.edsfair.com/2009/pdf/sp_s04/eds09_sp04_1.pdf

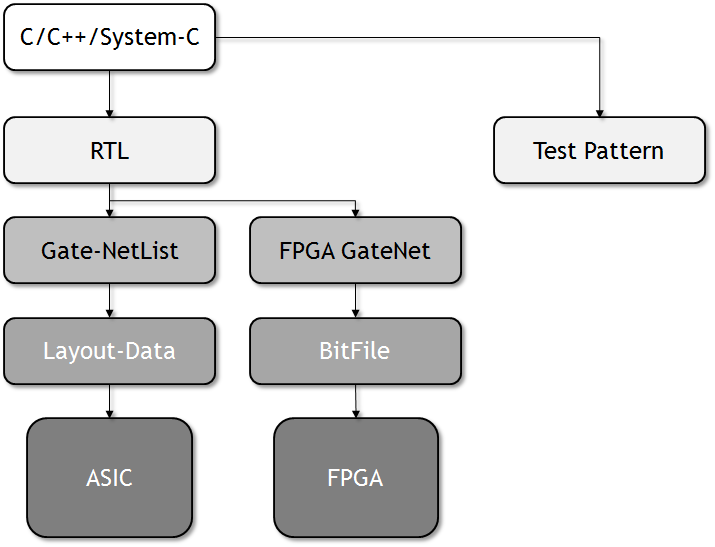

とある。動作記述、つまり「どのようなことを行いたいか?」を記述したら回路(それもRTLレベル)を生成する技術というように捉えることが出来る。

2. いろんな高位合成ツール

私の調査した限りでの、高位合成ツールをリストアップしてみる。

大体以下のような感じかなあ。いまいち高位合成ツールの比較方法って分からないんだよな。対象言語と値段くらいしか思いつかない。

あと、この一覧表は私のGoogle検索の結果と思い付く限りで調査したものなので、ウソや過不足もあると思うので、適宜ツッコミを入れて頂ければ助かります。

| Cyber Work Bench | Vivado-HLS | Catapult C | Impulse C | Synphony C Compiler | C-to-Silicon Compiler | |

|---|---|---|---|---|---|---|

| 開発元 | NEC | Xilinx | Mentor Graphics | Impulse Accelerated Technologies | Synopsis | Cadence |

| 対象言語 | System-C/ANSI-C | C/C++ | ANSI C++/System C | ANSI C | C/C++ | System C |

| 値段 | 有料 | 無償版あり | 有料 | 有料 | 有料 | 有料 |

CyberWorkBench

NECの開発した高位合成ツール。結構昔からある気がする。ハードウェアC(?)からRTLを生成することが出来る。有料だし非常にお高いと聞いているので、トライしたことは無い。

Vivado-HLS

https://japan.xilinx.com/products/design-tools/vivado/integration/esl-design.htmljapan.xilinx.com

Xilinxの発表したFPGA向け高位合成ツール。というかもとはAutoESLという高位合成ツールを買収したものらしい。C/C++からRTLを生成することが出来る。最近無料になった。

Catapult C

メンターグラフィックスの開発した高位合成ツール。C/C++などのからRTLを生成することが出来る。ちなみに、MicrosoftのProject Catapultとは関係無い。

Impulse C

こちらもFPGA向け、C/C++からRTLを生成する高位合成ツール。こちらは、何故か日本語の資料や書籍が入手しやすい。結構誰にでもトライアルできるツールなのかな?

![[実践] C言語による組込みプログラミングスタートブック [実践] C言語による組込みプログラミングスタートブック](https://images-fe.ssl-images-amazon.com/images/I/5104C6A8Z6L._SL160_.jpg)

- 作者: 鳥海佳孝

- 出版社/メーカー: 技術評論社

- 発売日: 2006/10/07

- メディア: 大型本

- クリック: 2回

- この商品を含むブログを見る

- 作者: デビッドペレリン,スコットティボー,天野英晴,David Pellerin,Scott Thibault,宮島敬明

- 出版社/メーカー: エスアイビーアクセス

- 発売日: 2011/08

- メディア: 単行本

- クリック: 18回

- この商品を含むブログ (1件) を見る

上記の書籍の翻訳は慶応大学の学生さんが行ったそうだ。すごいなあ。

Synphony C Compiler

Synopsysの高位合成ツール。C/C++をRTLにコンパイルする。