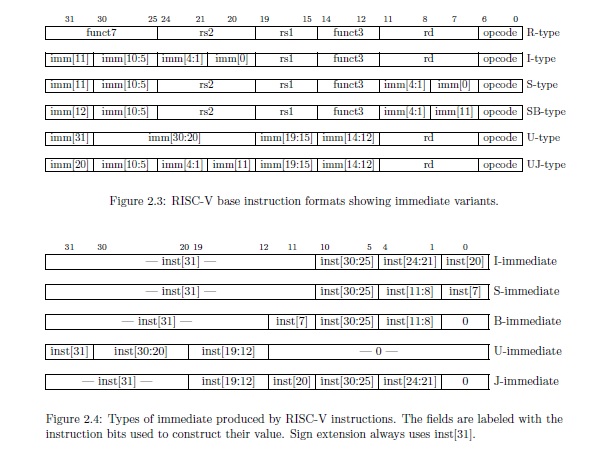

RISC-Vは即値生成のフォーマットがちょっと変わっている。MIPSとかなら、即値フィールドは下位の16ビットなどにまとめらているのだが、 RISC-Vは一見不思議に見える。以下がRISC-Vの即値生成フォーマットだ。

これ、よくよく説明を読むと、フィールド[10:5]とフィールド[4:1]の部分の選択肢は

- inst[30:25]

- inst[11:8] / inst[24:21]

しかない。 つまり、即値を生成するときに、この部分部分で独立して生成すれば、即値生成論理を簡単にすることができる、ということか。 でも、これの影響で、即値のデコーダはかなり苦しい。ISSを作っていても、バイナリから即値がすぐに計算できないというのは時としてはがゆい。

MIPSは割と簡単に計算可能、SHはかなり簡単にレジスタ値と即値を計算可能だ (SHはレジスタが16本しかないので、それも読み取りやすい)。 一方で難解なのはV850だ。気になる方は是非命令フィールドを見て欲しい。