Rocket-Chipにハイパーバイザ拡張実装するにあたり参考にされている論文があるので読んでみることにした。 11ページとまあまあ量があるので2~3回に分けて読んでまとめていくことにする。

A First Look at RISC-V Virtualization from an Embedded Systems Perspective

Abstract

Rocket-Chipへのハイパーバイザー拡張仕様 (H拡張 v0.6.1)を実装し、スタティックパーティショニングハイパーバイザであるBaoをRISC-Vに移植して動作させた。

FiresimとZynq UltraScale+ MPSoC ZCU104へ導入して動作させた。

このハードウェア実装はオープンソース化され、H拡張の批准に向けて使用されている。

イントロダクション

この10年間で、仮想化によるシステムの統合の需要はますます高まっており、そのための様々な技術が存在する。仮想マシンでは様々なアーキテクチャ資源(ラストレベルキャッシュ・インターコネクト・メモリコントローラなど)を共有するようになっている。

本論文は以下のことを行っている:

- RISC-V H拡張の最新バージョン(v0.6.1)をRocket Chipコアに初めてオープンソースで実装した(3.1節)。

- ハードウェアの強化により、仮想化サポートを調整(3.2節)。

- オープンソースのBaoハイパーバイザーのRISC-Vへの移植(4章)。

- ハイパーバイザー仕様の細かな機能のraw検証を可能にする、オープンソースのアドホックテストフレームワークの開発(5.1節)

- RISC-VコアにおけるH拡張の初の公開およびサイクル精度な評価。我々は、ハードウェアコスト、性能オーバーヘッド、VM間干渉、および割り込みレイテンシに着目しました(5節)。

2. RISC-V仮想化サポート

RISC-Vの仕様はもともとモジュール化できるように設計されており、このISAの仮想化に適した設計により、従来の手法(フルトラップ&エミュレート、シャドーページテーブルなど)に則したハイパーバイザーの実装や、本節で後述するハイパーバイザー拡張のエミュレーションをマシンモードから容易に行うことができる。

しかし、このような技術は、大きなパフォーマンス・オーバーヘッドを伴うことがよく知られている。

2.1 ハイパーバイザ拡張

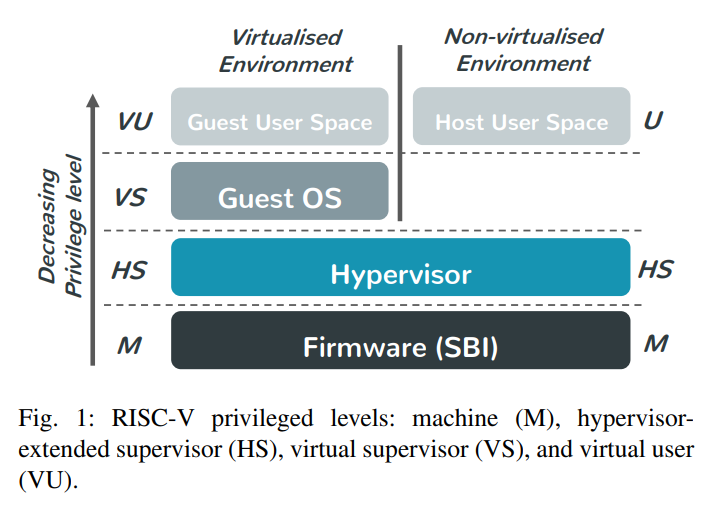

RISC-VのH拡張は、図1に示すようにスーパバイザモードをハイパーバイザ拡張スーパバイザモード(Hypervisor-extended supervisor mode: HSモード)に変更する。この拡張機能では、ゲストの物理アドレスとホストの物理アドレスをマッピングするページテーブルをハイパーバイザーが制御する2段階のアドレス変換も行う。

仮想化の制御は、暗黙的に定義されているVビットを付かttえ制御されている。Vビットが設定されているときは、VUモードまたはVSモードで実行される。

このH拡張では、いくつかの新しいハイパーバイザ命令とCSRが定義されている。例えば、hstatusはハイパーバイザーが仮想マシンの例外動作を追跡・制御することを可能にし、hgatpは第2ステージのルートページテーブルを指し、hfence命令はゲストのトランスレーションに関連するTLBエントリの無効化が可能となる。

H拡張で導入された革新的なメカニズムとして、ハイパーバイザ仮想マシンのロードストア命令である。ハイパーバイザはゲストの仮想アドレス空間に直接アクセスすることが出来るようになる。

また、ハイパーバイザ拡張では、VSモードでの実行をサポートするために、例外のトラップエンコードが増強されている。例えば、2番目のMMUでの変換が失敗した場合の例外や、ハイパーバイザコールに相当するVSレベルのECALLが追加されている。

また、今回は仮想化のネストについては対象外とする。

3. 実装

RocketChipにハイパーバイザを実装するが、今回はRV64のみを対象とすることにする。Rocket-Chipの実装に対してWithHypコンフィグを追加することで実現できる。

3.1 Rocket Coreハイパーバイザ拡張

Rocket-Coreについて、H拡張で実装すべき点はCSRモジュールの実装である。CSRのモジュールをH拡張用に実装したが、いくつかの機能は省略してある(例えばhtinstとmtinstはゼロに固定されている)。

表1に、実装されている機能と実装されていない機能をまとめている。

次に、MMUのPage Table Walkerを拡張してハイパーバイザの2段ページ変換をサポートした。ステートマシンを追加し、第1段階での変換が終了すると第2段階に移行するようにした。個々の実装は非常に困難で、いくつかの実装は省略されている。

最もコアの内部まで突っ込んで改造を行う必要があったのは、ハイパーバイザ仮想マシンのロードストア命令のサポートだった。特定の命令に対応してアクセス許可を変更できるような構成にはなっていないため、データTLBからL1キャッシュラインまでに、メモリアクセスのパーミッションを通知する信号を追加した。

また、物理アドレス空間のサポートSv39x4まで拡張した。

3.2 割り込み仮想化の向上

RISC-Vにはタイマーの仕様としてmtimeとmtimecmpレジスタが定義されているが、ハイパーバイザ拡張においてはこれを複数独立に確保し、特権レベルであるHSとVSが直接利用できるようにする飛鳥があった。この方法は例えばArmv8-Aアーキテクチャでも採用されており、すべての特権レベルとセキュリティ状態に渡って独立したタイマレジスタが定義されている。

CLINTにはstime, stimecmpレジスタ、vstime, vstimecmpメモリマップドレジスタを追加し、htimedeltaレジスタも追加した。htimedeltaをmtimeの値に加算することでvstimeの値に反映さている。

公式の仕様の検討も同時に行われ、私たちの実装とほぼ同様な仕様が検討されている。重要なのは、mtime系のレジスタはMMIOとして実装されており、各HARTで共有されているという点である。新しく実装したタイマはmtimeに依存しているため同様にMMIOとして実装し、タイマの実装をシンプルにした。

PLICは現在ほとんどのRISC-Vシステムで用いられている外部割り込みコントローラである。PLICは最大で1023個のデバイス割込みラインが接続され、割り込み有効レジスタ、・割込み処理のためのレジスタが定義されている。

ハイパーバイザ拡張のゲスト外部割込み機能を活用することで、システム性能とレイテンシを改善できるPLIC仕様の拡張を提案した。

- ハイパーバイザの介入なしに,アクティブなVSモードhartへの物理的割り込みの直接割り当てと注入を可能にす ること

- ハイパーバイザへのトラップを最小限に抑えること, 特にクレーム/コンプリートレジスタアクセス時のトラップを排除す ること

- 特定のVMに対して純粋な仮想割り込みと物理的割り込みの 混在を可能にすること

- ハードウェアの追加コストを限定し,全体的な複雑さを抑えた最小限の設計を行うこと

これらに対応するPLICの設計を行った。