RISC-VのアウトオブオーダコアであるBOOM (Berkely Out-of-Order Machine) について勉強を進めている。以下のドキュメントを日本語に訳しながら読んでいくことにした。

The Berkeley Out-of-Order Machine (BOOM)

Berkeley Out-of-Order Machine (BOOM)は,MIPS R10000 1 やAlpha 21264 2 のアウトオブオーダー・プロセッサに大きく影響を受けています。 MIPS R10000やAlpha 21264と同様に、BOOMも統一された物理レジスタファイル設計です(「明示的レジスタリネーミング」としても知られています)。

BOOMは、オープンソースの RISC-V ISA を実装し、 Chisel というハードウェア構築言語を利用して、コアのジェネレータを構築します。 ジェネレータは、RTL設計の一般化と考えることができます。 標準的なRTLデザインは、ジェネレーターデザインの1つのインスタンスとみなすことができます。 したがって、BOOMは、コアの単一のインスタンスではなく、アウトオブオーダーデザインのファミリーです。 さらに、BOOMコアでSoCを構築するために、BOOMは、異なるマイクロアーキテクチャ構造(TLB、PTWなど)を再利用するためのライブラリとして、 Rocket Chip SoCジェネレータを利用しています。

- 1 Yeager, Kenneth C. “The MIPS R10000 superscalar microprocessor.” IEEE micro 16.2 (1996): 28-41.

- 2 Kessler, Richard E. “The alpha 21264 microprocessor.” IEEE micro 19.2 (1999): 24-36.

BOOMパイプライン

概要

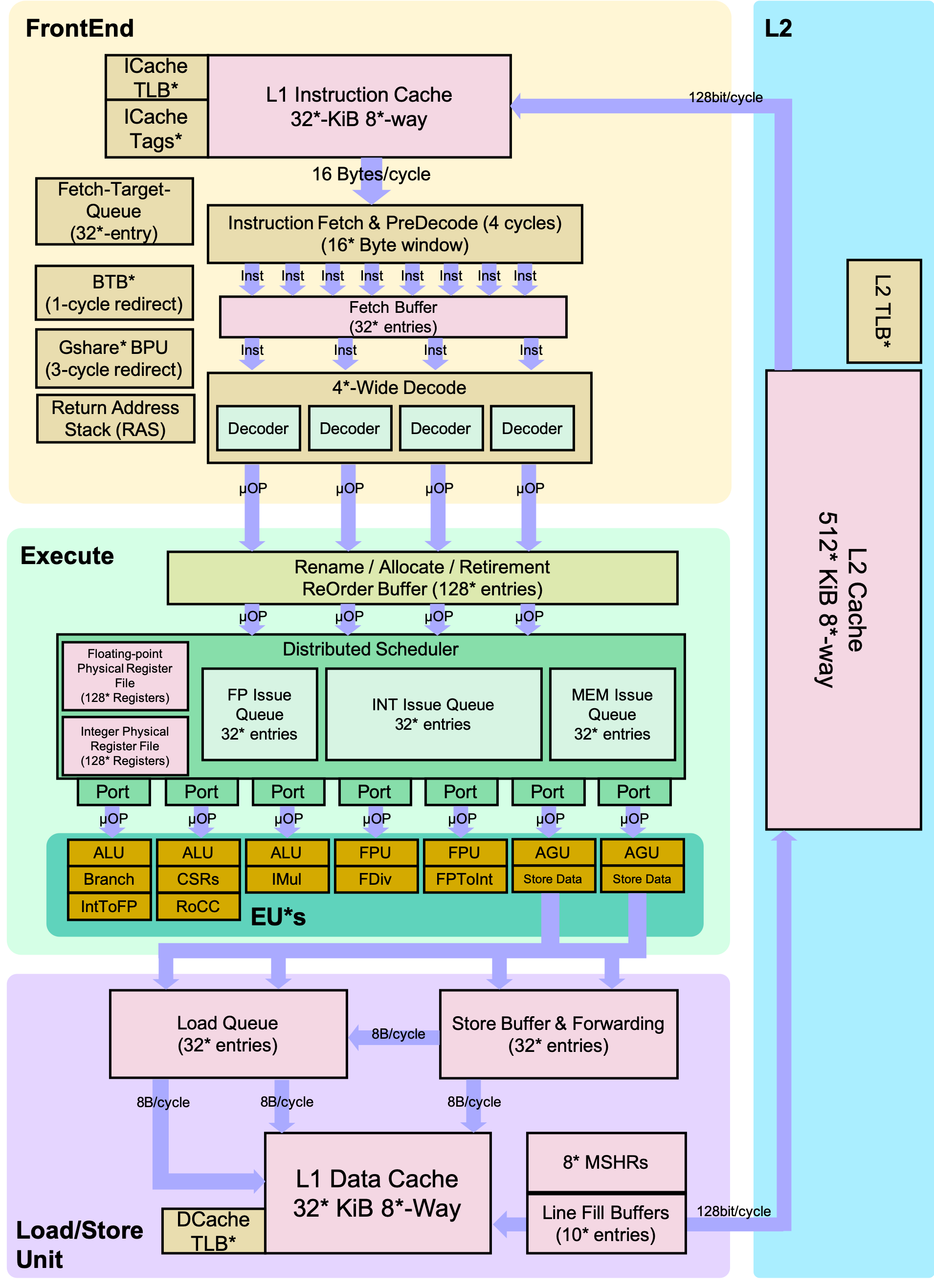

概念的に、BOOMは10のステージに分かれています。 フェッチ、 デコード、 レジスタリネーム、 ディスパッチ、 命令発行、 レジスタ読み込み、 実行、 メモリアクセス。 ライトバック、 コミット の順になります。しかし、これらのステージの多くは、現在の実装では 現在の実装では、これらのステージの多くが組み合わされ、 7 ステージとなっています。 フェッチ、 デコード・リネーム、 リネーム・ディスパッチ、 命令発行・レジスタ読み込み、 実行。 メモリ と ライトバック ( コミット は非同期に行われるため、「パイプライン」の一部としてはカウントされません)。 Fig. 2 は、すべてのパイプラインステージが記載されている簡略化された BOOM パイプラインを示しています。

ステージ

フェッチ

命令は、命令メモリからフェッチされ、 フェッチバッファ と呼ばれるFIFOキューに押し込まれます。 分岐予測もこの段階で行われ、フェッチされた命令を必要に応じてリダイレクトします。1

デコード

デコード は Fetch Buffer から命令を取り出し、 適切な Micro-Op(s) (UOPs) を生成してパイプラインに配置します。2

リネーム

ISA、つまり「論理的」なレジスタ指定(例:x0-x31)は、「物理的」なレジスタ指定子にリネームされます。

ディスパッチ

その後、 UOP は、 命令キュー のセットに ディスパッチ されるか、または書き込まれます。

命令発行

Issue Queue に置かれた UOPs<Micro-Op (UOP)> は、 そのオペランドの準備がすべてととのうまで待機し、その後 発行 されます。3 これがパイプラインのアウトオブオーダー部分の始まりです。

レジスタ読み込み

発酵された UOPs sは、まずレジスタ・オペランドを統一された 物理レジスタファイル (または バイパスネットワーク )から 読み込み ます。

実行

発酵された命令は、機能ユニットが存在する 実行 ステージに入ります。 発行されたメモリ・オペレーションは、実行 ステージでアドレス計算を行い、 メモリ ステージにある ロードストアユニット に計算されたアドレスを格納します。

メモリ

ロード/ストアユニット は、 ロードアドレスキュー(LAQ) 、 ストアアドレスキュー(SAQ) 、 ストアデータキュー(SDQ) の3つのキューで構成されています。 ロードは,そのアドレスが LAQ に存在するときにメモリに送られます。 ストアは、コミット 時にメモリに起動されます (当然ながら、ストアのアドレスとデータの両方が SAQ と SDQ に配置されるまで、ストアをコミットすることはできません)。

ライトバック

ALUオペレーションとロード操作は 物理レジスタファイル に ライトバック されます。

コミット

リオーダバッファ(ROB) は、パイプライン内の各命令の状態を追跡します。 ROBの先頭がビジーでない場合、ROBはその命令をコミットします。 ストアの場合、 ROB は ストアキュー(SAQ/SDQ) の先頭にあるストアに、 データをメモリに書き込めるようになったことを知らせます。

分岐のサポート

BOOMは完全な投機実行と分岐予測をサポートしています。 各命令は、それがパイプラインのどの位置にあるかに関わらず、 分岐タグ を伴っており、 その命令がどの分岐に対して”投機実行されている”のかを示しています。 分岐予測を誤ると、その分岐に依存していたすべての命令を殺す必要があります。 分岐命令が リネーム を通過する際には、レジスタリネームテーブル と フリーリスト のコピーが作成されます。 分岐予測に失敗した際には、保存されていたプロセッサの状態が復元されます。

詳細なBOOMのパイプライン

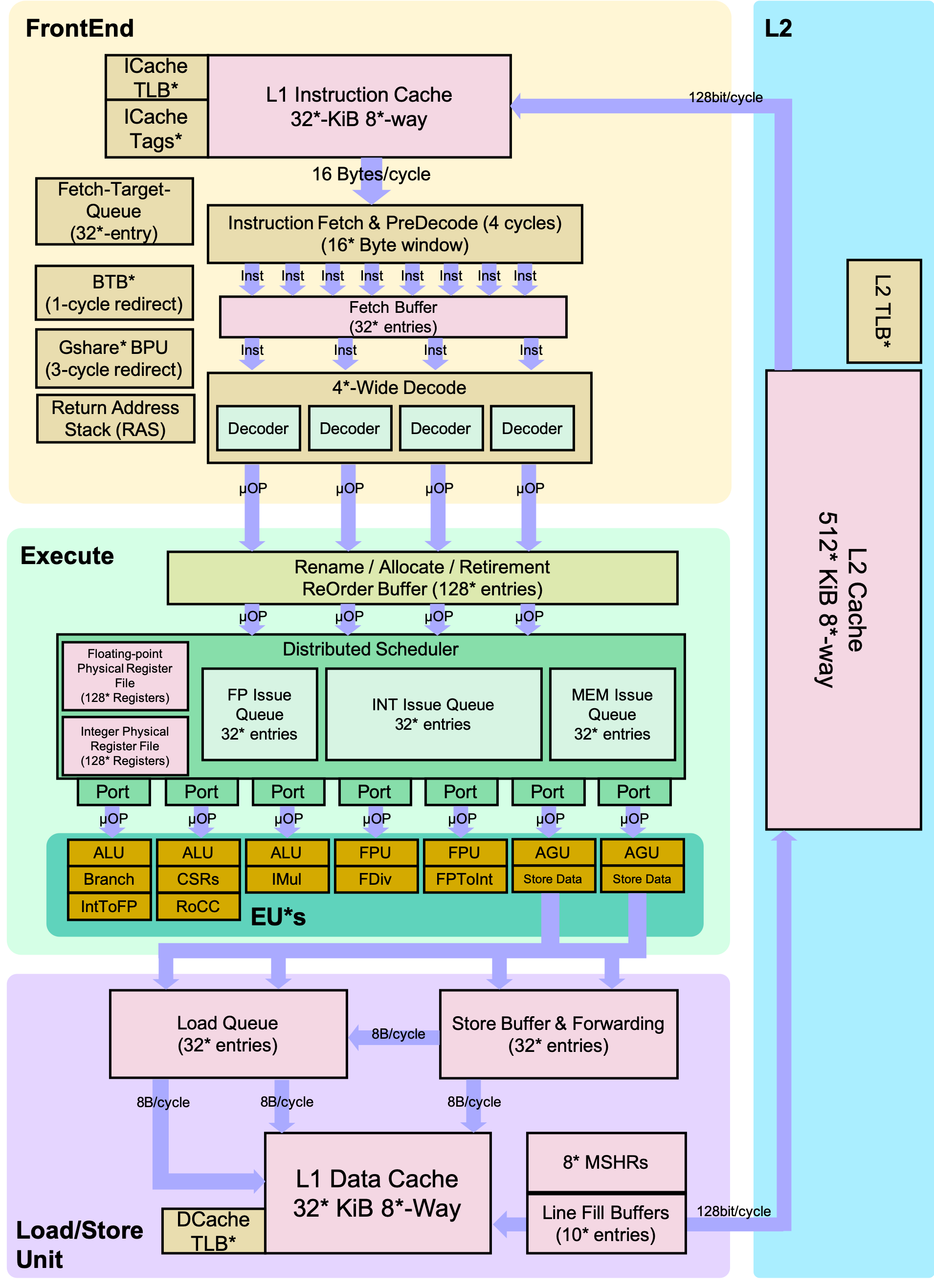

Fig. 2 は 簡略化されたBOOM パイプラインを示していますが、 BOOM は RV64GC と特権 ISA をサポートしており、単精度および倍精度の浮動小数点、アトミックのサポート、 ページベースの仮想メモリが含まれています。 より詳細な図は、以下の Fig. 3 にあります。

1 : フェッチバッファ は

Nエントリの深さがありますが、FIFO の先頭命令を即座に読み出すことができます。 別の言い方をすれば、命令の前に命令がなければ、 命令が フェッチバッファ を通過するのにNサイクルを費やす必要はありません。2 : RISC-VはRISC ISAであるため、現在、すべての命令は単一の Micro-Op (UOP) のみを生成します。 ストアの UOPs がどのように処理されるかについての詳細は、 The Memory System and the Data-cache Shim にあります。

3 : より正確には、準備が整った Micro-Ops (UOP) が要求をアサートし、命令キュー内の命令スケジューラが そのサイクルで発行する UOP を選択します。

ハードウェア構築言語Chisel

BOOMは、ハードウェア構築言語Chisel で実装されています。 ChiselはScalaに組み込まれたDSLで、高度にパラメータ化されたジェネレータを用いた高度なハードウェア設計をサポートしています。 Chiselは、学術界( Rocket Chip , FireSim など) や産業界 (Google Edge TPU ) の複数のプロジェクトで使用されています。

より詳細な情報は http://chisel-lang.org から参照できます。