TLBの挙動についてある程度分かるようになってきたので、実際の波形を見ながら解析してみたいと思う。ChipyardのBOOMコンフィグレーションで、RISC-Vテストパタンを走らせて波形を解析する。

./simulator-chipyard-MediumBoomConfig-debug \ --vcd=rv64ui-v-simple.medium.vcd \ --verbose ~/riscv64/riscv64-unknown-elf/share/riscv-tests/isa/rv64ui-v-simple rv64ui-v-simple 2>&1 \ | tee rv64ui-v-simple.log

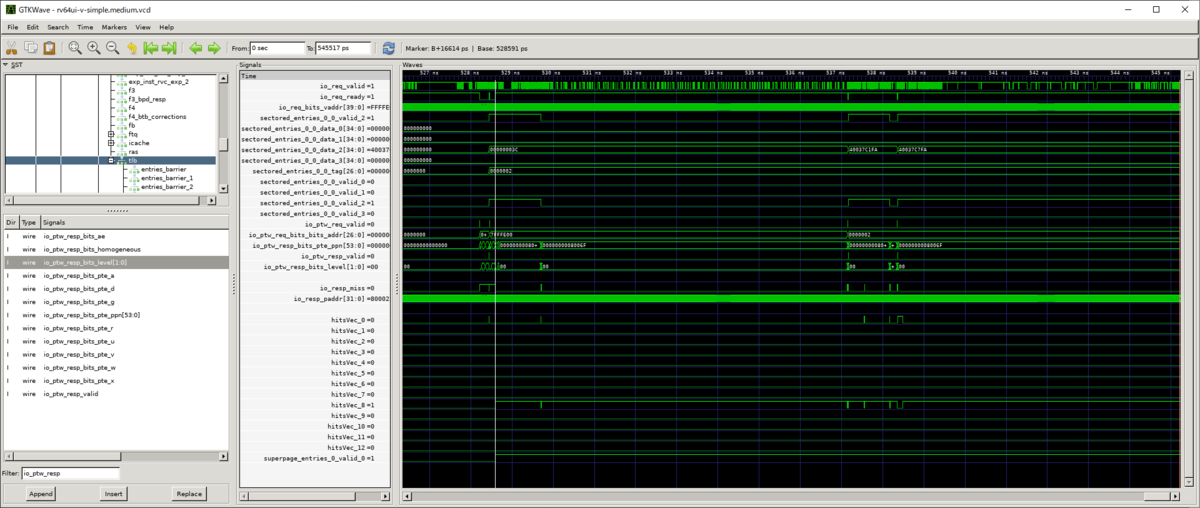

波形を取得したのでGTKWaveで表示してみる。だいたいこんな感じだ。

10265 1 0xffffffffffe02258 DASM(0x0000006f)

10266 1 0xffffffffffe02258 DASM(0x0000006f)

10267 1 0xffffffffffe02258 DASM(0x0000006f)

10268 1 0xffffffffffe02258 DASM(0x0000006f)

10269 1 0xffffffffffe02258 DASM(0x0000006f)

10270 1 0xffffffffffe02258 DASM(0x0000006f)

10271 1 0xffffffffffe02258 DASM(0x0000006f)

10272 1 0xffffffffffe02258 DASM(0x0000006f)

*** PASSED *** Completed after 272759 cycles

[UART] UART0 is here (stdin/stdout).

まず最初にTLBのエントリが有効化されるのは、最初にU-ModeでのTLBアクセスが行われたときだ。ユーザモードに切り替えられて最初のリクエストで、TLBのエントリのどれにもヒットしないのでPage Table Walkが発生する。

Page Table Walkのレスポンスにより、sectoroed_entries[0]が有効化されて以降のアクセスからはヒットし始める。

もう一つのパタンは、Page Table Walkの最中にSuperPage (最後のLeaf Tableまで行かずにPTEに到達した場合)にヒットした場合は、setored_entriesに格納せずにsuperpage_entriesに配置される。こちらもヒットしたときの挙動はsectored_entriesと同一だ。