Chiselを使って、非常にシンプルなCPUを作ってみるプロジェクト。 とりあえず、rv64ui-pのリグレッションテストがすべてPass するようになったのでGitHub上に公開した。

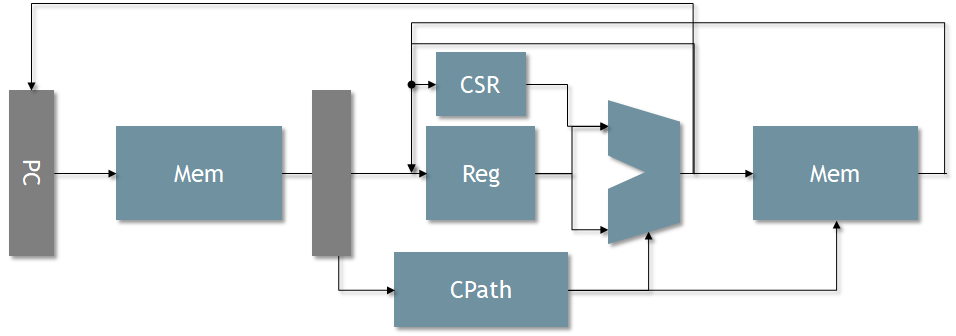

といっても、2段ステージのパイプラインで非常にしょぼいものだが。

ただし、このデザインの凄いところは一切Verilogを使っていないこと。だいたいのChiselのデザインはメモリのところにVerilogを使ったり、 CPUの動作制御の部分にVerilogを使ったりするのだが、これは全てChiselで記述してある。 したがって、Verilogに変換することなくシミュレーションを走らせることができ、Verilogシミュレータを使うことなく高速にシミュレーションできる。

リグレッションテストを流してみるが、せっかくなのですべてのテストをScala環境で流せるようにしたい。

まず、実施したいテスト向けにテストコードを自動生成するようなスクリプトを作成した。 以下のようなファイルが、テストパタンの数だけ生成される。

cd tests/riscv-tests/isa make # テストパタンを生成する。 ruby ./gen_test_class.rb

src/test/scala/cpu/Test_rv64ui-p-add.scala

package cpu import chisel3.iotesters import chisel3.iotesters.{ChiselFlatSpec, Driver, PeekPokeTester} class Tester_rv64ui_p_add extends ChiselFlatSpec { "Basic test using Driver.execute" should "be used as an alternative way to run specification" in { implicit val conf = RV64IConf() iotesters.Driver.execute(Array(), () => new CpuTop()) { c => new CpuTopTests(c, "tests/riscv-tests/isa/rv64ui-p-add.hex", "pipetrace.rv64ui_p_add.log") } should be (true) } }

Makefileはテストパタンの数だけターゲットが作られる。

riscv64_make.mk

... test_run_rv64ui_p_add: sbt 'testOnly cpu.Tester_rv64ui_p_add -- -z Basic' test_run_rv64ui_p_addi: sbt 'testOnly cpu.Tester_rv64ui_p_addi -- -z Basic' test_run_rv64ui_p_addiw: sbt 'testOnly cpu.Tester_rv64ui_p_addiw -- -z Basic' test_run_rv64ui_p_addw: sbt 'testOnly cpu.Tester_rv64ui_p_addw -- -z Basic' test_run_rv64ui_p_and: sbt 'testOnly cpu.Tester_rv64ui_p_and -- -z Basic'

これにより、make test_run_rv64ui_p_addにより単体のテストを流すことができるようになった。結果のログはpipetrace.rv64ui_p_add.logに保存されるので、spike-dasmによりディスアセンブルを行う。

spike-dasm < pipetrace.rv64ui_p_add.log > pipetrace.rv64ui_p_add.dasm.log

あと、全てテストパタンを流すためにはmake regressionを入力することでテストできる。

今のところ、64ビットモードの整数テストは全てPassしている。 次は、これをパイプラインを挿入して5段くらいまで拡張して、徐々に性能を上げていきたい。