RISC-VのNVDLAがコラボしたり、NVDLAの調査も再度実施しなければならないと思ってきた。

テストパタンの中で、sanity1 / sanity2 BDMAのテストパタンだ。 BDMAはいわゆるDMAのことなのだが、ディープラーニング向けのDMAよろしく、いろんな設定ができるようになっている。

まずは、sanity2のテストパタンのテストの内容をチェックしていこう。

Feature Dataという入力データを外部から取り込んで、別のメモリ場所に格納するというDMAのテストである。

Feature Dataはsample_surf.datというデータに格納されている。これはreadmemhでcsb_master_seqというモジュール経由であらかじめ外部メモリに格納されているものとする。

load_mem 0x80000000 0x1000 sample_surf.dat

テストパタンの内容としては、0x80000000から格納されているsample_surf.datのデータを0x81000000にDMA転送するというものである。

この時に幾つかパラメータを設定するのだが、その前にFeature Dataの構造について理解しておく必要がある。

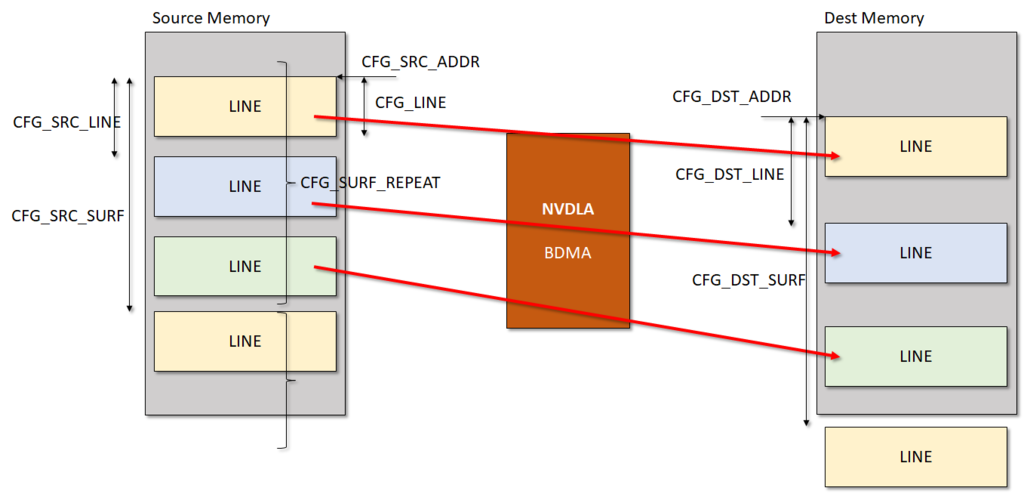

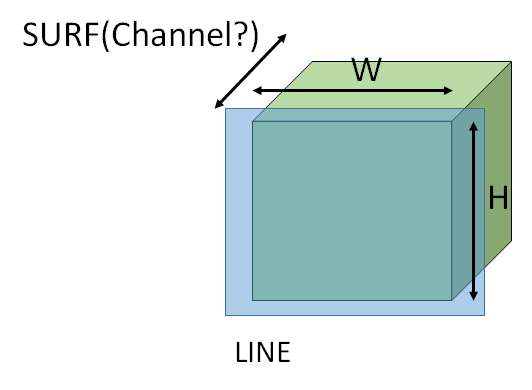

パラメータには大きく分けて"LINE"向け、"SURFACE"向けのパラメータが存在している。 マニュアルを読んだ感じだと、

- LINE : Feature DataのW(Width)×H(Height)に相当するデータ群

- SURF : Feature DataのC(Channel)に相当するデータ群

であると理解した。これらについて、BDMAでは転送ストライドをそれぞれ設定しながらデータを流すことができるというわけだ。

転送パラメータについて確認しよう。

- SURF向けの設定

CFG_SRC_SURF_0: SURFのSource Addressのストライド数。この1SURF(=Channel)は、ここで設定したバイト数の間隔で配置されているものとする。- テストパタン : 0x800 (つまりSURFは0x800バイト毎に配置されている)

CFG_DST_SURF_0: SURFのDestination Addressのストライド数。- テストパタン : 0x800 (つまりSURFは0x800バイト毎に転送する。)

CFG_SURF_REPEAT_0: SURFを何ブロック分転送するかを示している。ここでは0が設定されているので1回分転送する。

- LINE向けの設定

CFG_SRC_LINE_0: LINEのSource Addressのストライド数。この1LINE(=W×H)は、ここで設定したバイト数の間隔で配置されているものとする。- テストパタン : 0x100 (つまりLINEは0x100バイト毎に配置されている)

CFG_DST_LINE_0: LINEのDestination Addressのストライド数。- テストパタン : 0x100 (つまりLINEは0x100バイト毎の場所に転送される)

CFG_LINE_0: 1LINEのサイズを指定する。ここでは7が設定されているので8(=7+1)×32-byte(256-bit)が転送される。CFG_LINE_REPEAT_0: LINEを何ブロック転送するかを示している。ここでは7が設定されているので8(=7+1)回LINEが転送される。

それぞれの関係図を示すと以下のようになる。3次元の入力データに対して、このようにして自由に転送できる領域を変えている。