RISC-VのCompressed命令について理解したので、自作ISSへの実装を進めた。

Compressed 命令の仕様については以下のまとめた。

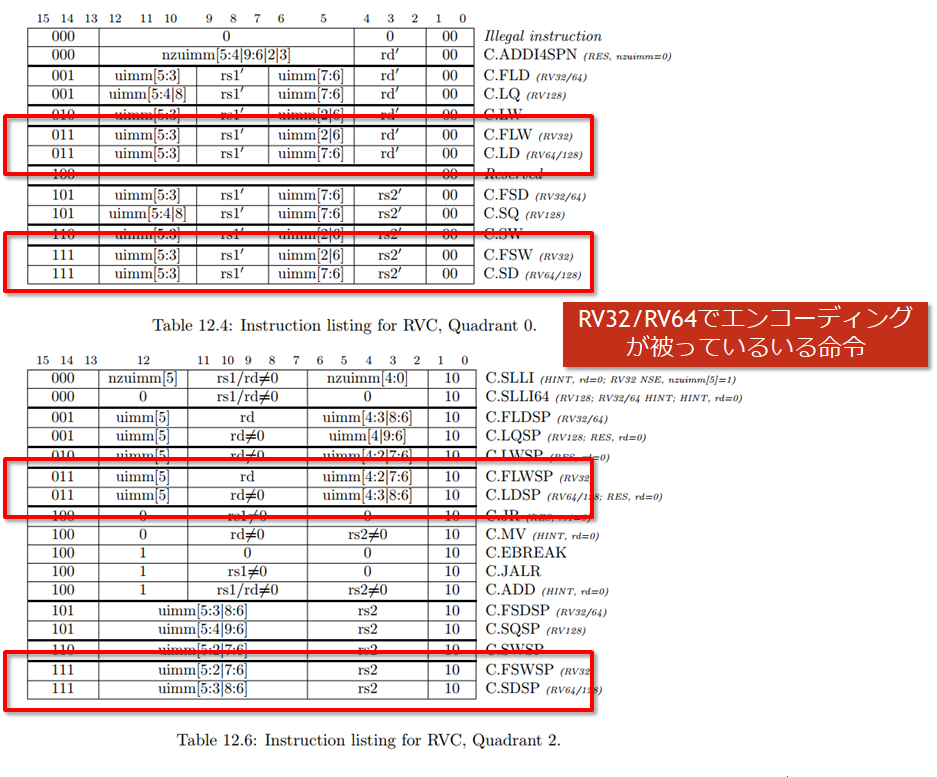

前回のRV64版のCompressed命令の実装についてはとりあえず終わったので、次はRV32版のCompressed命令の実装を検討していた。

RV64とRV32で命令エンコーディングがかぶっている部分があるのでこれをどうしようかなと思っていたのだが、よく考えてみると 別にすべて自動で生成する必要は無くて、被っている2命令だけはモードに応じて手動でデコードしてやればいいんだ。 なんだ、単純。

というわけで、最後までデコードした後に、かぶっている命令については手動でデコードする関数を追加した。

// Remaining Instruction is 2 // c.fswsp f[6:2],u[9:7]|u[12:10]<<3 // c.sdsp r[6:2],u[9:7]|u[12:10]<<3 return DecodeInst_LD_10_F3_110_R3_00000_F2_00_R2_00000_R1_00001_RD_00000_OP_00000 (inst); break;

で、最後のDecodeInst_LD_10_F3_110_R3_00000_F2_00_R2_00000_R1_00001_RD_00000_OP_00000という関数は自分で書いてやる。

ここだけは特殊なデコードを許す。

InstId_t RiscvDec::DecodeInst_LD_10_F3_110_R3_00000_F2_00_R2_00000_R1_00001_RD_00000_OP_00000 (InstWord_t inst_hex)

{

if (FLAGS_bit_mode == 32) {

return InstId_t::INST_ID_C_FSWSP;

} else if (FLAGS_bit_mode == 64) {

return InstId_t::INST_ID_C_SDSP;

} else {

return InstId_t::INST_ID_SENTINEL_MAX;

}

}

というわけで、無事にRV32/RV64のどちらでもテストがPassするようになった。とりあえずCompressed命令の実装はこれで終わり。