RISC-Vの実装であるHummingBirdを調査していくことにした。

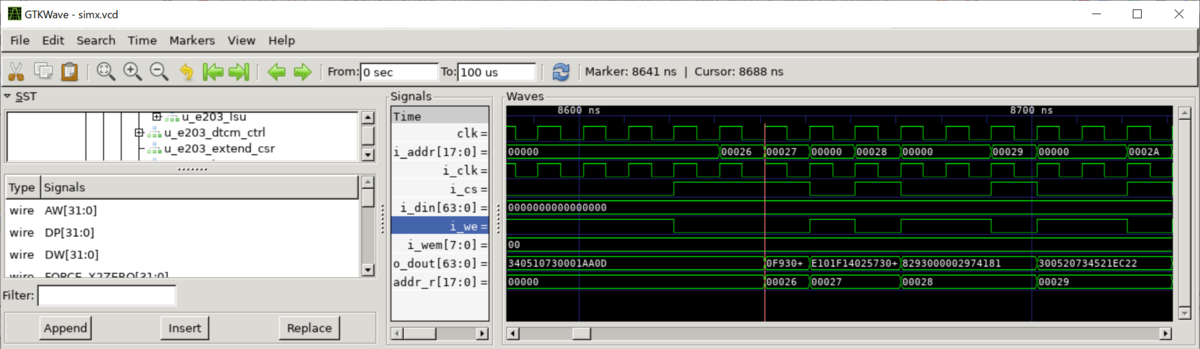

Verilatorでのデバッグを行っているのだが、どうも上手く動いてくれていない。波形を見てもなんだか動いていないように見えるので、Verilatorでクロックゲーティングをすると何かおかしくなるのだろうか?まずは基本的なところが動いてほしいので、クロックゲーティングをすべて停止してみる。

rtl/e203/core/e203_clkgate.v

diff --git a/rtl/e203/core/e203_clkgate.v b/rtl/e203/core/e203_clkgate.v index bd3a456..a29451d 100644 --- a/rtl/e203/core/e203_clkgate.v +++ b/rtl/e203/core/e203_clkgate.v @@ -45,9 +45,9 @@ always@(*) if (!clk_in) enb = (clock_en | test_mode); -assign clk_out = enb & clk_in; +// assign clk_out = enb & clk_in; +assign clk_out = clk_in; `endif//} endmodule

すると何となく動いているような気がしてきた。しかしまだシミュレーションが終了しない。テストパタンも途中で止まっているように見えるのだが、何か繰り返して待ち状態に入っているような気がする。wait_loop1というルーチンは何のために待ち合わせをしているんだ?

80000192: 0000100f fence.i 80000196: 000012b7 lui t0,0x1 8000019a: a0028293 addi t0,t0,-1536 # a00 <_start-0x7ffff600> 8000019e <waitloop1>: 8000019e: 12fd addi t0,t0,-1 800001a0: fe029fe3 bnez t0,8000019e <waitloop1> 800001a4: 100083b7 lui t2,0x10008 800001a8: 00838393 addi t2,t2,8 # 10008008 <_start-0x6fff7ff8> 800001ac: 0003a283 lw t0,0(t2)

一応ループは回っているようなのだが、何をしているのか、パイプラインがなんの命令を実行しているのかさっぱりわからないので、例によってパイプライントレーサを作り込んだ方が良いのではないかという気がしてきた。 そのあたりから取り組もうかな。