"The RISC-V Instruction Set Manual. Volume II: Privileged ISA Document Version 20190608-Priv-MSU-Ratified" が公開されてしばらくたったのだが、少し時間ができたので変更点の部分を簡単に調べてみることにした。

各モードの状態について。

| Module | Version | Status |

|---|---|---|

| Machine ISA | 1.11 | Ratified |

| Supervisor ISA | 1.11 | Ratified |

| Hypervisor ISA | 0.3 | Draft |

Prefaceによる、仕様の改定部分は以下。

- Machine ISAおよびSupervisor ISAの仕様を"Ratified"ステータスに変更。

- 説明と解説の改善。

- Hypervisor ISA拡張のDraftを追加。

- どの割り込みソースが標準使用のために予約されているかを記載。

- カスタム使用のためにいくつかの同期例外の原因の割り当て。

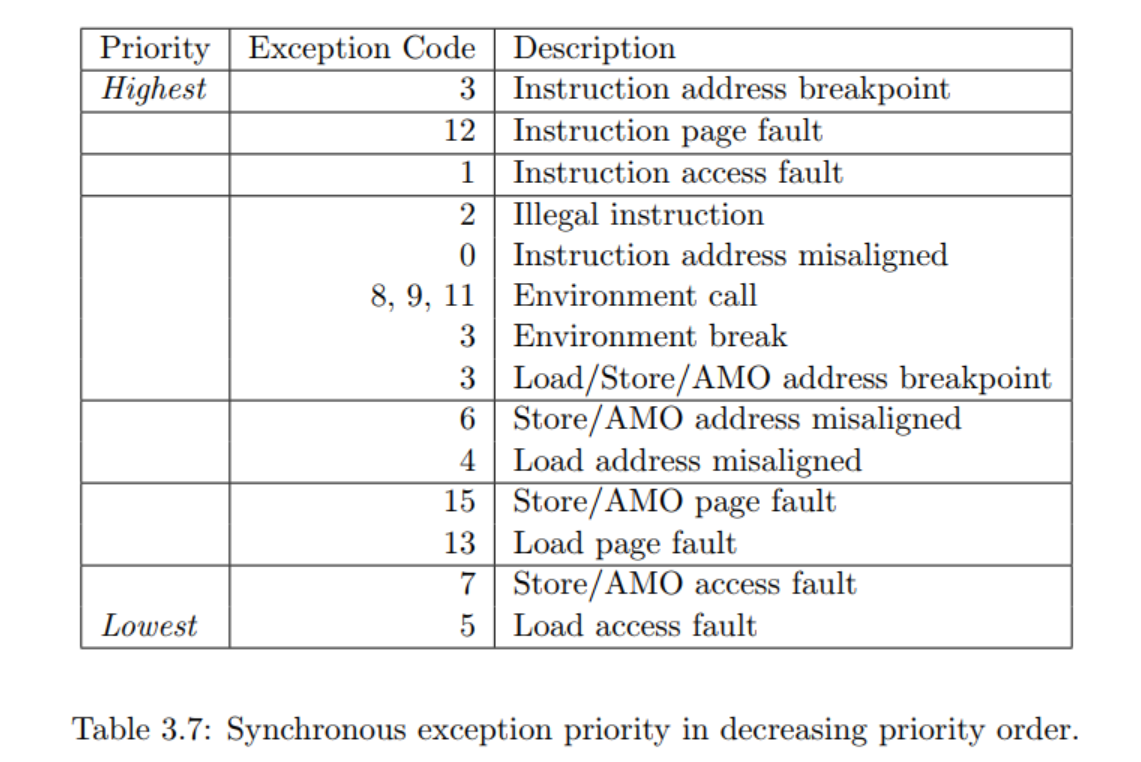

- 同期例外の優先順位を記載。

- "A"拡張が存在する場合、xRET命令がLR予約をクリアすることができるが

- ただし必須ではない。

- SUMの設定に関係なく、仮想メモリシステムは、スーパーバイザモードがユーザページからの命令を実行することを許可しないように変更。

- 将来の拡張でASIDをグローバル化してパフォーマンスとハードウェアの柔軟性を向上させることができるように、ソフトウェアでASIDをグローバルに割り当てることを強く推奨する。

SFENCE.VMAのセマンティクスを明確化。mstatus.MPPフィールドがWLRLからWARLに変更。xipのうち未使用のフィールドをWIRIからWPRIに変更。misaの未使用のフィールドをWIRIからWLRLに変更。pmpaddrおよびpmpcfgの未使用のフィールドをWIRIからWARLに変更。- システム内のすべてのHartが互いに同じPTE更新スキームを採用する必要があることを記載。

- 例外が発生したときに

mstatus.xIEが書き込まれるメカニズムについて説明の誤りを修正。 - ミスアラインした場合のAMOをエミュレートするためのスキームを説明。

- 変数

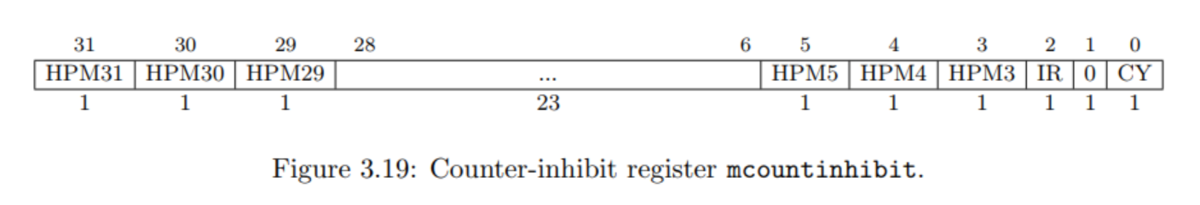

IALIGNを使用して、システムのmisaおよびxepcレジスタの動作を記載。 misaレジスタに矛盾する値を書き込む動作を指定。mcountinhibitCSRを定義。これは、パフォーマンスカウンタのインクリメントを止めて、消費電力の増大を防ぐ。- 4バイトより粗いPMP領域のセマンティクスを記載。

XLENの変更に関するCSRの動作について記載。- PLICについての記載を分離。

新たな割り込み要因の追加

カスタム命令などで利用できる例外の要因の追加。

| Interrupt | Exception Code | Description |

|---|---|---|

| 1 | 0 | User software interrupt |

| 1 | 1 | Supervisor software interrupt |

| 1 | 2 | Reserved for future standard use |

| 1 | 3 | Machine software interrupt |

| 1 | 4 | User timer interrupt |

| 1 | 5 | Supervisor timer interrupt |

| 1 | 6 | Reserved for future standard use |

| 1 | 7 | Machine timer interrupt |

| 1 | 8 | User external interrupt |

| 1 | 9 | Supervisor external interrupt |

| 1 | 10 | Reserved for future standard use |

| 1 | 11 | Machine external interrupt |

| 1 | 12–15 | Reserved for future standard use |

| 1 | ≥16 | Reserved for platform use |

| 0 | 0 | Instruction address misaligned |

| 0 | 1 | Instruction access fault |

| 0 | 2 | Illegal instruction |

| 0 | 3 | Breakpoint |

| 0 | 4 | Load address misaligned |

| 0 | 5 | Load access fault |

| 0 | 6 | Store/AMO address misaligned |

| 0 | 7 | Store/AMO access fault |

| 0 | 8 | Environment call from U-mode |

| 0 | 9 | Environment call from S-mode |

| 0 | 10 | Reserved |

| 0 | 11 | Environment call from M-mode |

| 0 | 12 | Instruction page fault |

| 0 | 13 | Load page fault |

| 0 | 14 | Reserved for future standard use |

| 0 | 15 | Store/AMO page fault |

| 0 | 16–23 | Reserved for future standard use |

| 0 | 24–31 | Reserved for custom use |

| 0 | 32–47 | Reserved for future standard use |

| 0 | 48–63 | Reserved for custom use |

| 0 | ≥64 | Reserved for future standard use |

割り込み・例外の優先順位

CSRの各フィールドの表記について

| 正常値書き込み | 不正地書き込み | 読み込み | 備考 | |

|---|---|---|---|---|

| Reserved Writes Ignored, Reads Ignore Values (WIRI) | 無視される | 無視される | デフォルト値が読まれる。 ソフトウェアは無視する必要がある。 | 将来の予約フィールド |

| Reserved Writes Preserve Values, Reads Ignore Values (WPRI) | 読み込んだ値を保持するようにストアする必要がある | 読み込んだ値を保持するようにストアする必要がある | 書き込んだ値が読まれる | 将来の予約フィールド |

| Write/Read Only Legal Values (WLRL) | 正常書き込み | 不正書き込み | 正常に書いた場合は正常に読み込まれる。不正書き込み後は値は不定となる | |

| Write Any Values, Reads Legal Values (WARL) | 正常書き込み | 不正書き込み | 不正書き込みをしても正常な値が読まれる。 |

Machine Counter-Inhibit CSR(mcountinhibit)