Rocket Chipのバス設計は非常に読み解くのが難しい。 Rocket Chipのフロントエンドを読み解いていこうと思ったが、フロントエンドのバス接続の部分でさっそく挫折してしまった。

特に、Chiselで記述されたバスプロトコルとLazyModuleを読み解くのが何だか良く分からない。前提知識ゼロで臨むのは厳しいので、基本的な知識を身に着けるために論文を読み始めた。

- Diplomatic Design Patterns: A TileLink Case Study

まずは前半部分。DiplomacyとTileLinkについて。

現代のSoC設計において、バスの接続というのは非常に時間がかかるもので、かつミスを起こしやすい。そこで、RISC-VベースのRocket-Chip GeneratorではInterconnectsを接続する環境を構築した。

Rocket-ChipのTileLinkの実装は、Diplomacyを使用して構築している。

1. Introduction

現代のSoC設計について、バス設計というのはとにかく大変なものである。

Rocket ChipのSoCを構築するために、2種類のツールを開発した。

Diplomacyプロトコルのキモ:パラメタライズおよびネゴシエーションのためのフレームワークである。

- マスタースレーブのペアとプロトコルのテンプレートを与えることで、Diplomacyはすべての接続されたデバイスの要件を確認し、設定可能なパラメータを確認し、最終的にアダプタとエンドポイントにバインドするパラメータを生成する。

- システムのエンドポイントで排他的なアクセスが生じることを確認するために、Diplomacyは他のエンドポイントの情報を使用する。

例として、TileLinkを取り上げる。TileLinkの特徴としては

- プロトコルは階層構成が可能

- トランザクションレベルでのデッドロックを生じさせない。

- Rocket ChipジェネレータでのTileLink実装はインターコネクト間でのヘテロジニアスなレベルのプロトコルを提供する。

ここでは、TileLinkとDiplomacyを使用することで、プロトコルのパラメータを手動で設定しない。

- システムインターコネクトのネットワークグラフからパラメータを推論する。

- さらに、キューの挿入などのリタイミングを容易に実現する。

2. Diplomacy

DiplomacyはRocket Chip内のSoCバスプロトコルを構築するためのフレームワークで、以下の2種類のコンポーネントが含まれている。

- Diplomacyのライブラリ

- プロトコルの実装

DiplomacyはChiselで設計してあり、Scalaの機能を使用してパラメタライズを行っている。これはVerilogのパラメタライズよりも柔軟で、より細かなパラメタライズしたVerilogを生成することができる。

Diplomacyでは、インターコネクトを有効グラフで構築する。Diplomacyでは、プロトコル間の仕様についてクロスチェックを行っている。

Diplomacyは、特定のデータや制御信号の幅などといったプロトコル内の任意のフリーなパラメータを自動的に設定することができる。

- 最初のフェーズではパラメータの交渉であり、グラフのトポロジを作りだし、ノードはすべてのエッジにおいてパラメータの値を設定する。

- 2番目のフェーズは具体的なモジュールの生成であり、Chiselのコンパイラが起動しノードグラフに応じてモジュールを生成する。各Chiselのモジュールはエラボレートされ、事前に計算されたDiplomaticなパラメータを使用して構築される。

Diplomacyは、インターコネクトの要素として「ノード」と「エッジ」を作成する。

- ノード : ハードウェアを生成するためにデザイン内のどこでDiplomaticなパラメータが使用されるかを表現する。

エッジ : マスターとスレーブのインタフェースの有向なペアを表現する。

ソース : マスターインタフェース

- シンク : スレーブインタフェース

パラメータは、ソースからシンクに伝搬(outward)、もしくはシンクからソースに伝搬(inward)される。

パラメータのネゴシエーションには2つのサブプロセスが存在する。

- ソースエンドポイントノードから始まり、いくつかのパラメータフローが全てのシンクノードに到達するまで続ける。

- シンクエンドポイントノードから始まり、全てのソースノードに対してパラメータが伝搬するまで続ける。

したがって、すべてのエッジが双方向からのすべてのパラメータを受け取ることになる。

Diplomacyはバスプロトコルからは独立であり、どのようなプロトコルでもDiplomaticのコンポーネントを使用して構築可能である。

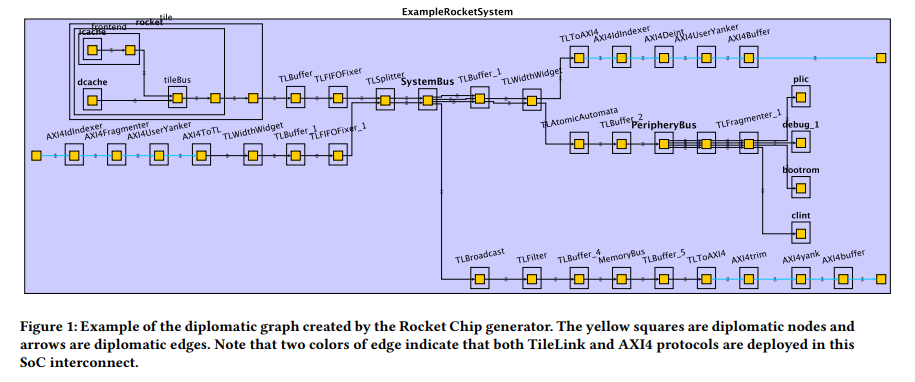

Figure-1はシンプルなRocket ChipのDiplomaticなグラフを示している。黄色い箱がDiplomaticなノードであり、⇔がDiplomaticエッジである。2色のエッジはTileLinkとAXI4プロトコルを示しており、SoCインターコネクト上にデプロイされる。AXI4はシステムの外部とコミュニケーションするために使用され、TileLinkは内部の接続のために使用される。左上のノードはRocketプロセッサの命令キャッシュとデータキャッシュである。左下のノードはAXI4からTileLinkへのブリッジである。図の中心部のノードのシーケンスうはブートROMやデバッグユニットなどのブロックである。2種類のTileLink-AXI4変換が搭載されており、キャッシュ可能なアクセスとアンキャッシュなアクセスをそれぞれ表現している。