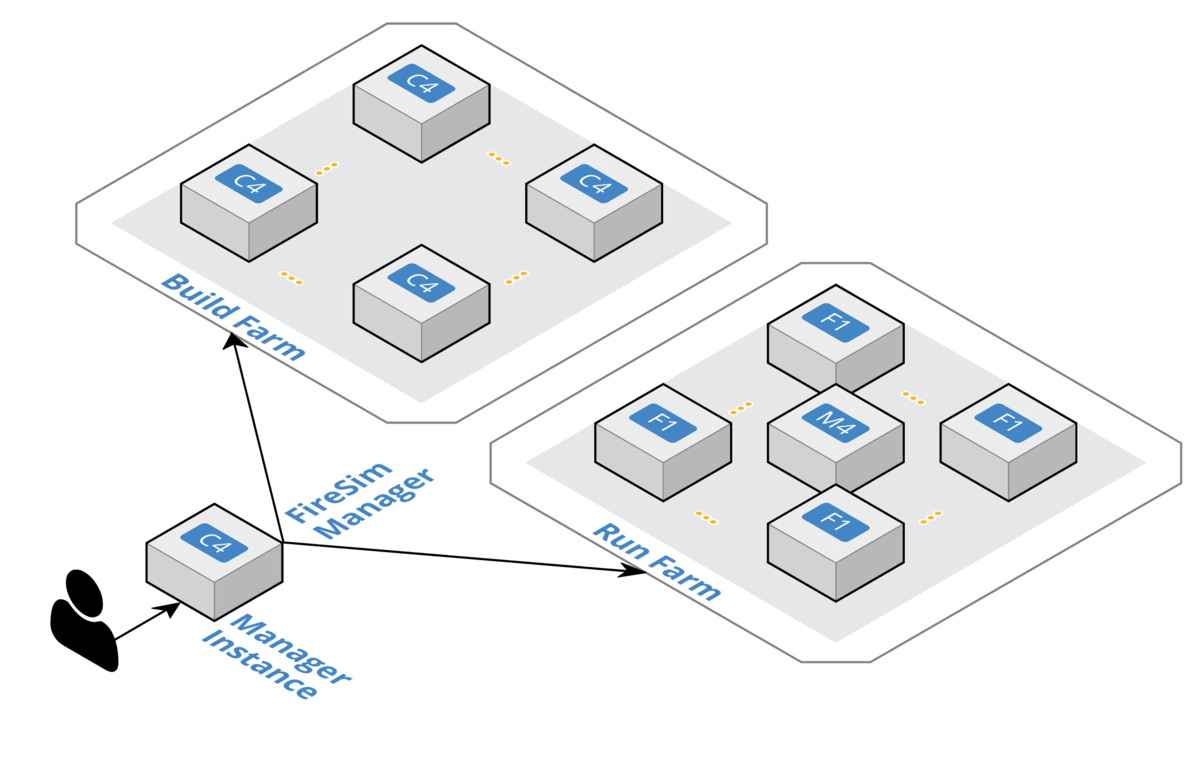

FireSimのシミュレーションに使用する独自のAFIイメージを作成する。

AFIとは、Amazon FPGA Imageの略称で、AFIを作成しておけばすぐにAWS f1インスタンスにデザインをデプロイできる。

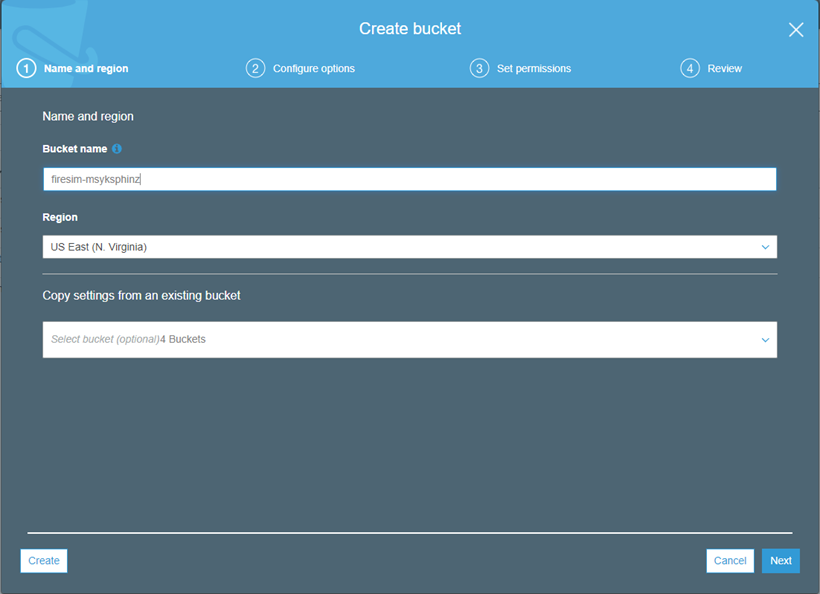

Amazon S3のアカウントをセットアップしていることを前提にする。 Amazon S3のコンソール上で[Create bucket]をクリックして新しいバケットをセットアップする。

[Bucket name]は"firesim-(アカウント名)"とする。 そうしないとfiresimがS3バケットを認識できない。 私の場合は、"firesim-msyksphinz"とした。次に[Next]をクリックする。

そのまま[Next]をクリックし続け、[Create Bucket]をクリックして新しいバケットを生成する。

S3上でバケットの構築が完了すると、次にマネージャインスタンス上で作業する。firesim/deploy/config_build.iniを編集する。

[afibuild] s3bucketname=firesim-msyksphinz [builds] # this section references builds defined in config_build_recipes.ini # if you add a build here, it will be built when you run buildafi firesim-singlecore-no-nic-lbp # #firesim-singlecore-nic-lbp # #firesim-quadcore-no-nic-lbp # #firesim-quadcore-nic-lbp # firesim-quadcore-no-nic-ddr3-llc4mb # firesim-quadcore-nic-ddr3-llc4mb # #fireboom-singlecore-no-nic-lbp # fireboom-singlecore-no-nic-ddr3-llc4mb # #fireboom-singlecore-nic-lbp # fireboom-singlecore-nic-ddr3-llc4mb # #firesim-supernode-singlecore-nic-ddr3-llc4mb # #firesim-supernode-quadcore-nic-ddr3-llc4mb # firesim-supernode-singlecore-nic-lbp [agfistoshare] firesim-singlecore-no-nic-lbp # #firesim-singlecore-nic-lbp # #firesim-quadcore-no-nic-lbp # #firesim-quadcore-nic-lbp # firesim-quadcore-no-nic-ddr3-llc4mb # firesim-quadcore-nic-ddr3-llc4mb # #fireboom-singlecore-no-nic-lbp # fireboom-singlecore-no-nic-ddr3-llc4mb # #fireboom-singlecore-nic-lbp # fireboom-singlecore-nic-ddr3-llc4mb # #firesim-supernode-singlecore-nic-ddr3-llc4mb # #firesim-supernode-quadcore-nic-ddr3-llc4mb # firesim-supernode-singlecore-nic-lbp

ターゲットとなるfiresim-singlecore-no-nic-lbpのみを残し、あとはコメントアウトする。

これをしっかり行わないと、ターゲットとなるイメージの数だけインスタンスが生成されてしまい、料金がかさむことになってしまう。

上記のように編集した後、firesim buildafiを実行する。処理が完了するのに、3~4時間程度かかる。

途中で以下のようなメッセージが連発されるが、辛抱強く待つこと(筆者は我慢できずGitHub Issueで質問したら、「我慢しろ」という回答が返ってきた)。

Current state: pending Current state: pending Current state: pending Current state: pending Current state: pending ...

辛抱強く待つと、

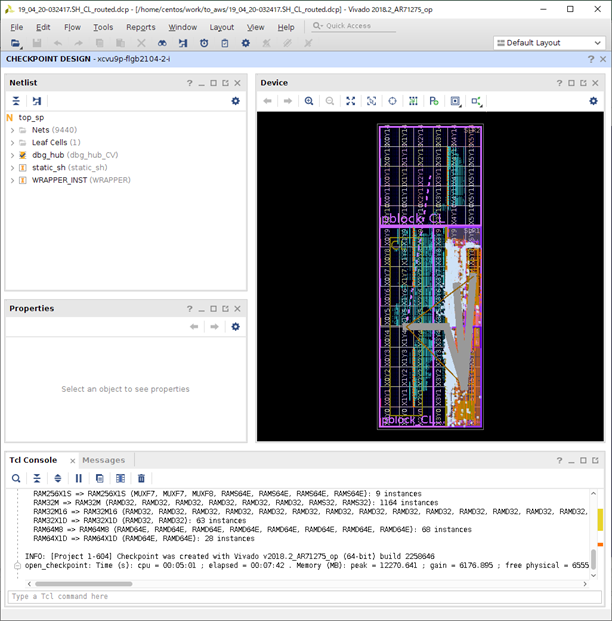

RTLの生成と、Vivadoでの論理合成とイメージの作成が行われ、その結果がS3に書き込まれる。 このイメージには、論理合成のログとVivadoのdcp(Design Check Point: プロジェクトファイルのようなもの)が格納されている。Vivadoでdcpファイルを開くと、どのようなデザインがどのようにFPGAにマッピングされたのかチェックできる。

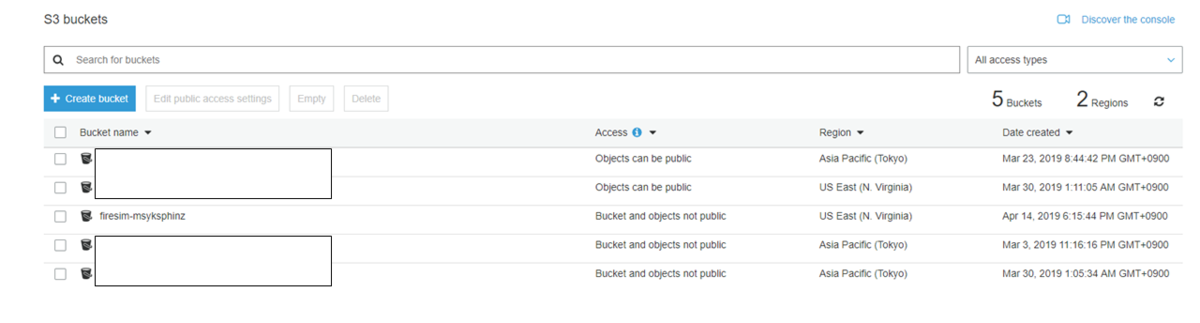

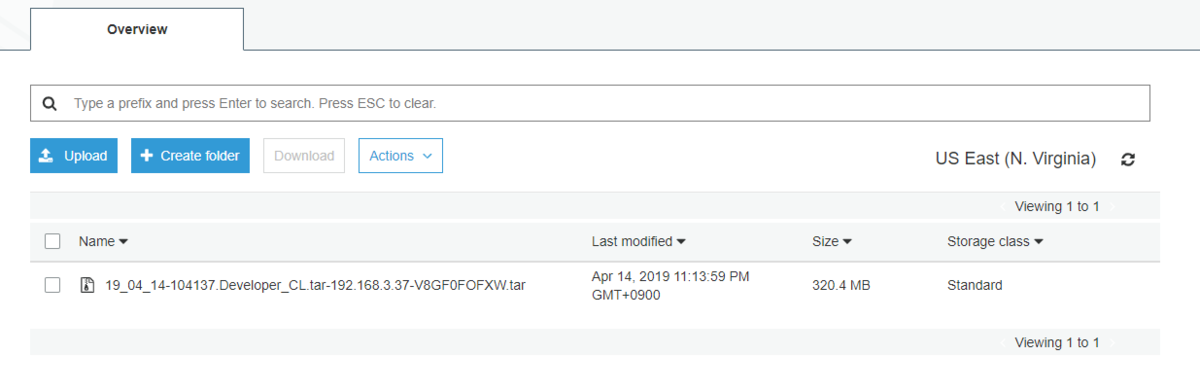

S3バケットを見てみる。"firesim-msyksphinz"バケットの中を覗いてみると、tarで圧縮されたファイルが格納されているのが分かると思う。

FireSimのFPGAイメージはS3バケットに格納されているので、基本的にどのインスタンスを使ってVivadoを立ち上げても構わない(つまり、日本から遠いNorth Virginiaのインスタンスを使わなくても、TokyoのインスタンスでFPGA Developer AMIを使ってインスタンスを立ち上げても問題ない)。しかし手っ取り早いのはFireSimのマネージャインスタンスを使う事だ。 AWSのコンフィグレーションも終わっているので、S3との連携も完了している。 なお、f1インスタンスで使用されているのは特殊なAWS用に開発された特殊なFPGAのようなので、FPGA Developer AMIに同梱されているVivado以外ではFPGAデバイスを認識できなかった。 手元のローカルマシンでdcpを開こうと何度も挑戦したのだが、うまくいかなかった。 やはり、AMI上のVivadoを使うのが最も安心のようだ。

念のため、VivadoをオープンするためにはGUIを使用するので、f1インスタンスにsshで接続している場合はX11のフォワーディングの設定をしておく。 筆者は以下のパッケージを追加でインストールする必要があった。

sudo yum install xorg-x11-xauth.x86_64 xorg-x11-server-utils.x86_64 dbus-x11.x86_64

さて、以下のようにしてS3上に格納されているVivadoのDCPをマネージャインスタンスのLinuxにダウンロードする。

aws s3 cp s3://firesim-msyksphinz/dcp/19_04_20-032417.Developer_CL.tar-192.168.4.9-VF6PT4V3DA.tar .

tarを解凍し、dcpをオープンする。

tar xf 19_04_20-032417.Developer_CL.tar-192.168.4.9-VF6PT4V3DA.tar

cd to_aws

vivado 19_04_20-032417.SH_CL_routed.dcp

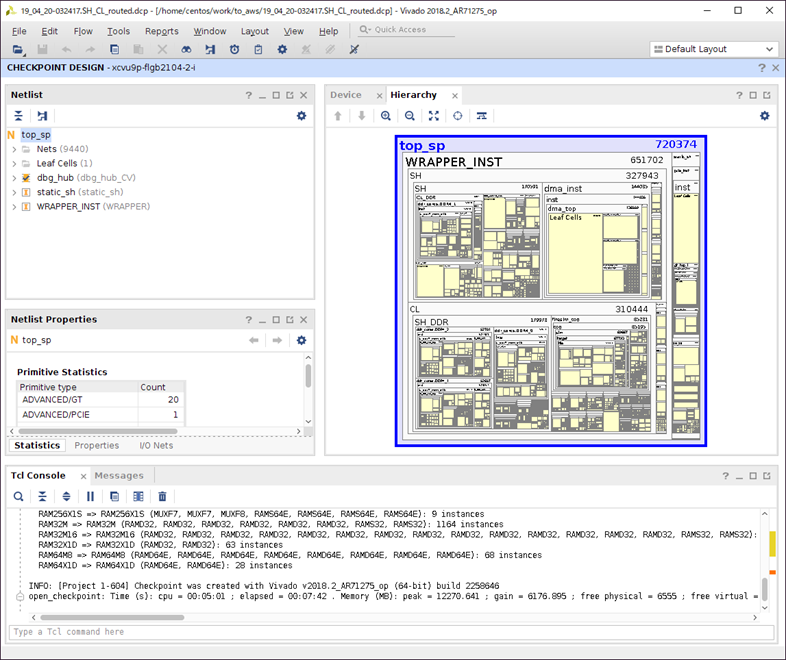

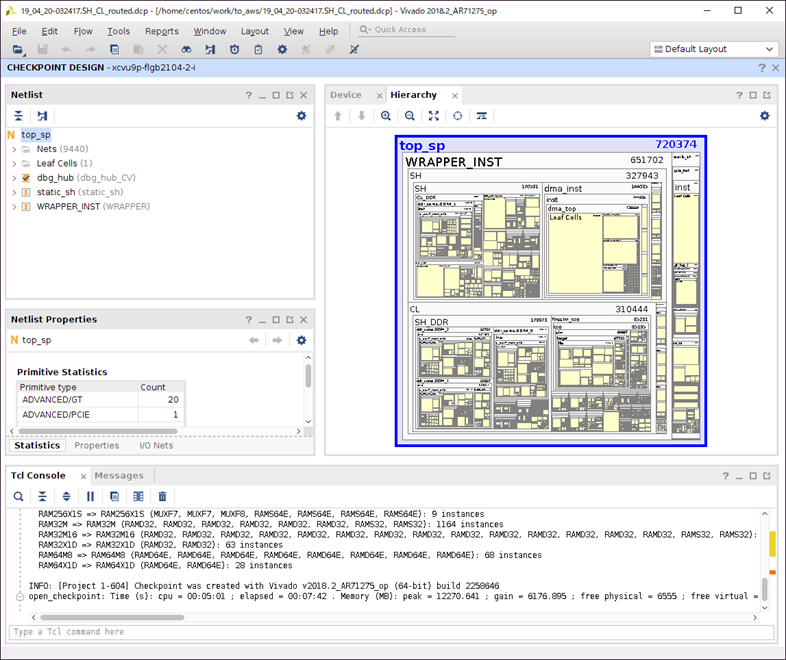

Vivadoがたちがあり、dcpをロードしている。 しばらくすると、以下のような画面になると思う。 FireSimが配置配線され、FPGA上にインスタンスされている様子が何となくだが分かると思う。

より詳細にブロックダイアグラムを見ていくと、どのようなモジュールがインスタンスされているのかわかると思う。FireSimはRISC-Vコアのほかに、PCI ExpressのモジュールやDDRのコントローラなどもインスタンスされていることが分かる。