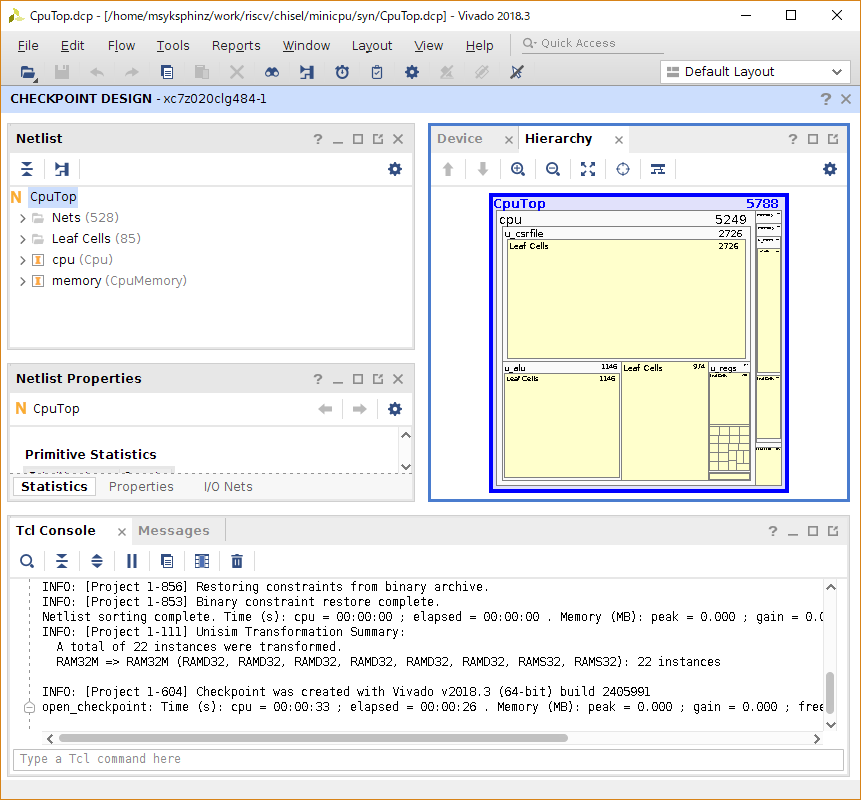

ChiselでRISC-Vプロセッサを設計するプロジェクト、しばらく手を付けていなかったのだが、実際にFPGAで動かすことを想定してVivadoで論理合成を実施した。

Vivadoの論理合成スクリプトは、まだCPUのIP単体だけなので単純に合成をするだけで配置配線までは行わない。

さらに、メモリの部分をBlackBoxでブロックRAMに置き換えるために、Verilogを生成している。

module MemoryResourceBox ( input logic clock, input logic io_mem_inst_bus_req, input logic [15:0] io_mem_inst_bus_addr, output logic io_mem_inst_bus_ack, ... memory_core #(.DATAW(64), .ADDRW(16)) u_mem ( .clock (clock), .addra(io_mem_data_bus_addr), ...

module memory_core #( parameter DATAW = 64, parameter ADDRW = 16 ) ( input logic clock, input logic [ADDRW-1: 0] addra, ...

無事に合成を完了することができた。

合成結果、BlockRAMからデータを読みだしたものをBlockRAMに書き出すパスが存在する?クリティカルパスとして現れてしまった。 動作周波数としては30MHz程度になってしまった、これは改善しないとなあ。